在先进逻辑工艺讨论中,我们很容易把注意力全部放在晶体管结构上:

FinFET、GAA、CFET……

但在 IEDM 2025 的这份 Short Course 报告中,IBM 给出的视角非常直接:晶体管还能继续演进,但互连已经开始成为决定系统性能的硬瓶颈。

这份报告的主题并不宏大,却极其现实: Cu 互连还能不能继续用?如果不能,下一步该怎么走?

一、先给结论:这不是“Cu 已死”的报告

报告一开始就把话说清楚了:

Cu 并没有立刻失效 但在先进节点下,Cu 必须被“系统性改造” 真正面向 1.x nm 及以下节点的方案,已经不能只靠 Cu 延寿

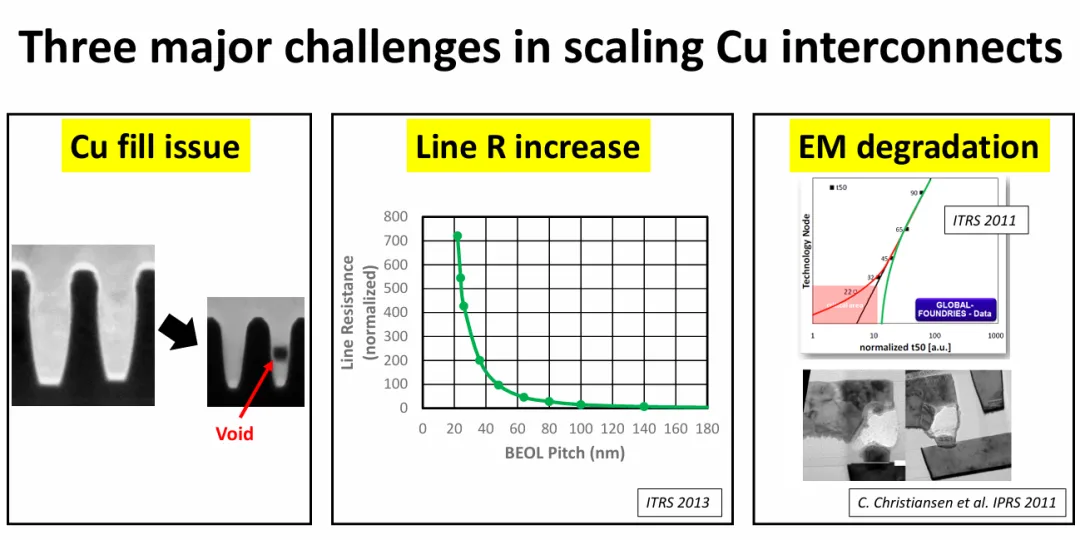

二、Cu 互连真正卡住的,不是某一个点

报告非常明确地指出:Cu 互连的问题不是单点失效,而是三件事同时恶化。

1. Cu 填充:已经接近几何极限

随着 BEOL pitch 持续缩小:

沟槽越来越窄 深宽比越来越高 Barrier / liner 越来越薄

结果是:

Cu electroplating 的填充窗口急剧收窄,空洞不再是“偶发缺陷”,而是结构性风险。

2. 线电阻上升:不是工艺没做好,而是物理必然

当线宽进入十几纳米:

Barrier / liner 占比不断增加 Cu 有效导电截面积不断下降 电子平均自由程与线宽同量级

这时,表面散射和晶界散射成为主导机制,Cu 的电阻率随尺寸缩小急剧上升。这不是“换个设备就能解决”的问题,而是尺寸效应本身在惩罚 Cu。

3. 电迁移:小空洞也能致命

在高电流密度条件下:

原子迁移路径变短 多个界面同时成为扩散通道

报告强调一个容易被低估的事实:

在先进节点,哪怕是很小的 EM 空洞,也足以在目标寿命内造成失效。

三、Cu Extension:不是换材料,而是“榨干体系潜力”

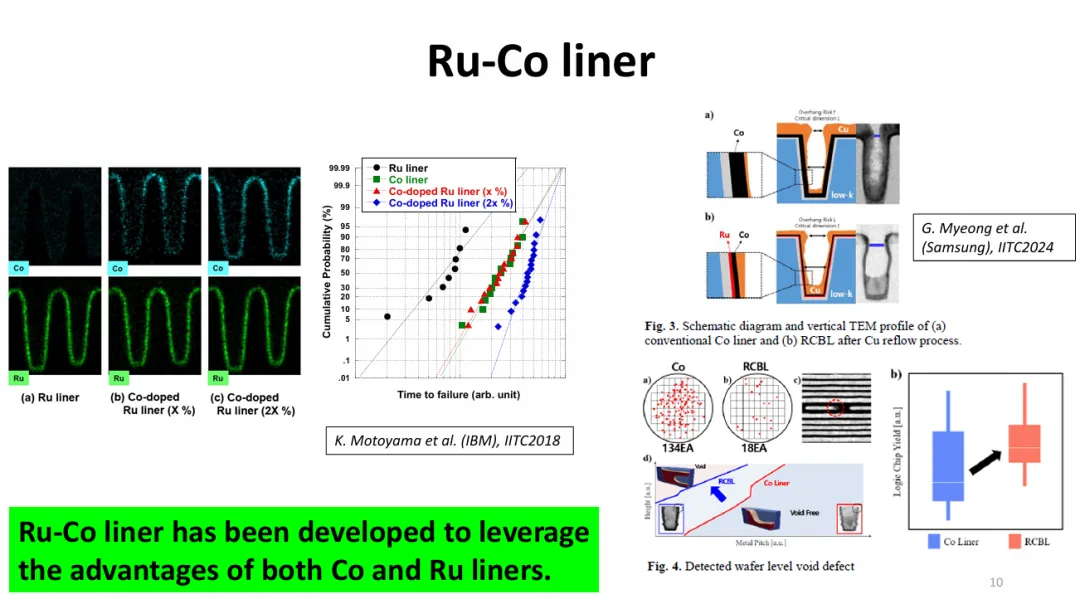

1. Liner 工程:从 Ta 走向 Ru-Co

报告回顾了 liner 的演进逻辑:

Ta/TaN:传统方案,已不适合极小尺寸 Co liner:显著改善 Cu fill Ru liner:填充能力更好,但带来 CMP 与 EM 新问题 Ru-Co 复合 liner:在填充、EM 和集成复杂度之间取得更平衡的结果

这是目前多家厂商都在验证、甚至已经采用的现实路径。

2. Cu Reflow:已经不是实验室技术

报告明确指出:

Cu reflow 自 7 nm 起具备量产可行性 相比传统 seed + plating: 晶粒更大 EM 寿命分布更集中 不是“最好”,但在极限条件下“更稳”

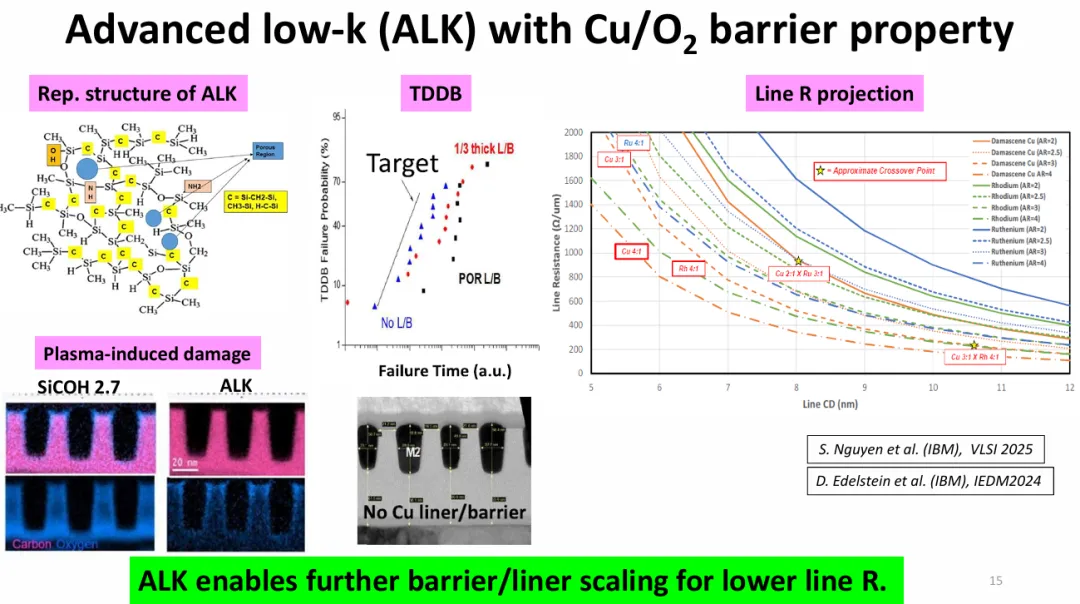

3. Advanced Low-k:为 Cu 多争取一点空间

一个容易被忽略的关键点是:

新一代 ALK 材料本身具备 Cu/O₂ barrier 特性 可以进一步减薄 liner 直接降低线电阻,同时维持 TDDB 可靠性

这不是低 k 回潮,而是Cu 能否继续用下去的重要前提。

四、真正的 Innovation:Post-Cu 不是“换金属”那么简单

报告给出了一个非常清醒的判断:

Post-Cu 的难点,不在于“选哪个金属”,而在于“你用什么互连架构”。

1. 为什么 Ru / Co 会成为候选?

报告给出的筛选标准非常工程化:

尺寸散射下的有效电阻率 高熔点与高内聚能(抑制 EM) 趋近 barrier-less 的集成潜力

在这些条件下,Ru、Co、Rh 成为现实候选,其中 Ru 的研究数据最完整、验证最系统。

2. Damascene Ru 的“隐藏问题”:Line Wiggling

这是整篇报告中非常“IEDM”的一个点。

在 Ru damascene 结构中,观察到沿线方向的周期性 CD 起伏(wiggling):

不是 litho 问题 不是刻蚀缺陷 而是高表面能金属 + 低模量 low-k 结构下的力学失稳

结果是:

局部强散射 有效电阻上升 设计不可预测

这直接动摇了 damascene 是否适合 Post-Cu 金属。

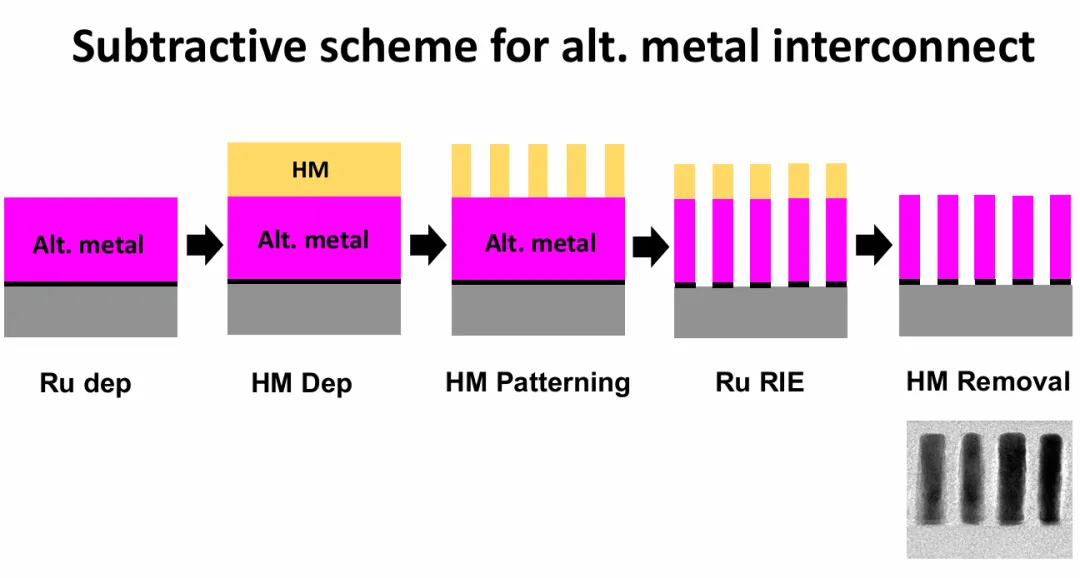

五、Subtractive Ru:报告给出的关键突破口

在此背景下,报告给出了一个非常明确的方向:

Post-Cu 必须认真考虑 Subtractive 工艺路线。

1. 为什么是 Subtractive?

相比 damascene:

导体体积分数更高 更容易引入 airgap Line / via 可以同时受益 R、C、EM 可以一起改善,而不是彼此牺牲

2. TopVia 结构的真正价值

Fully subtractive Ru TopVia 带来的不是“结构好看”,而是实打实的工程收益:

消除 line-via 接口 Via 导体体积最大化 Airgap 不再被 via 打穿 寄生电容降低约9–23%

3. 可靠性不是 PPT

报告给出了明确的实验结果:

TDDB:满足目标要求,无明显 spacing 依赖 EM:在相似尺寸下,优于已知 Cu damascene 数据 EM 失效位置出现在 Cu feeder,而非 Ru 本体

这意味着:Ru 本身并不是系统中的短板。

六、写在最后:这份报告真正想告诉我们的

这不是一份“预测未来”的报告,而是在回答一个现实问题:

如果今天就要往 1 nm 走,互连该怎么办?

IEDM 给出的答案非常务实:

Cu 仍然能用,但只能在“被极度优化的延续路线”中使用 真正面向未来节点的互连,必须接受: 材料改变 结构改变 集成方式改变 Subtractive Ru + TopVia + Airgap,是目前少数同时满足物理、工艺和可靠性的现实方案

晶体管还在往前冲,而互连,已经开始决定谁能真正走到终点。

如果您喜欢学芯屋的内容,想看到更多半导体芯片设计&制造相关的知识,可以点击“在看”、“转发”、“点赞”,并在评论区留言想学习的内容,博主会抽出时间加急更新,请点击下面的名片加关注并设星标,学芯屋知识星球会分享更多有价值的文献报告等等,欢迎各位加入!