随着人工智能(AI)与高效能运算(HPC)需求激增,晶圆代工产业的技术正迅速演进,以突破传统摩尔定律放缓的瓶颈。本报告针对五大前沿趋势进行探讨:(1)先进制程方面,目前3奈米技术领跑业界,2奈米及以下节点研发竞赛正酣,晶体管从FinFET迈向环绕栅极(GAA)架构,预期带来更佳性能与能效。 (2)先进封装技术蓬勃发展,包括2.5D矽中介层、3D晶片垂直堆叠,以及融合两者优势的3.5D架构,同时扇出型封装(FOWLP/FOPLP)在行动装置与IoT领域日益普及。这些封装突破让更多晶片整合在单一系统内,提升运算密度并降低功耗。 (3)异质整合成为新常态,透过先进封装将不同功能、不同制程的晶片(如处理器与高频记忆体)整合,大幅增强AI/HPC系统效能并改善良率与成本。 (4)材料创新方面,新兴材料如玻璃基板可望取代传统有机载板,解决热膨胀与讯号损耗问题,低介电材料降低讯号延迟,低碳材料与绿色制造则满足永续发展需求。 (5)全球主要业者积极布局未来:台积电持续稳居领先地位并扩产先进制程与封装;三星紧追其后,率先导入GAA技术并拓展自家异质整合方案;英特尔则重返先进节点竞局,规划18A制程量产与玻璃基板应用;其他业者如联电、格罗方德专注成熟制程市场、中芯国际(SMIC)在限制下推进7奈米技术、日本Rapidus与IBM合作挑战2奈米。

3纳米技术:截至2024年底,3nm已成为全球晶圆代工最先进的量产制程。台积电的N3(3纳米)制程自2022年下半年量产,并迅速成为公司先进制程营收主力之一:在2024年第4季,3纳米产品占台积电晶圆销售额的26%。台积电选择在3nm世代继续采用强化的FinFET晶体管技术,并透过FinFlex等技术提升性能/功耗表现。同时,三星电子于2022年6月宣布率先量产3nm制程,首度在代工业导入环绕栅极(GAA)晶体管架构。三星3nm采用多桥通道场效电晶体(MBCFET)技术,宣称相较7nm FinFET可降低45%功耗、提升性能并缩小晶片面积。然而,初期良率挑战使三星一度失去部分客户订单,但随着制程成熟,其3nm良率已提升到约六成水平(接近台积电同期的3/4nm良率)。

2纳米研发竞赛:展望2纳米节点,台积电、三星和英特尔三强正积极备战,预计将在2025年左右进入量产里程碑。台积电规划于2025年下半年开始2nm(N2)量产,2026年扩大量产规模。 N2将采用纳米片晶体管(nanosheet GAA),相较N3有显著性能与能效提升,根据国际电子元件会议(IEDM)发表数据,台积电2nm可比3nm降低30%功耗、提升15%速度。台积电同时着手布局2nm后的「Å世代」制程技术:首个后2nm节点(代号A16)将采用新一代纳米片电晶体,导入超级电源轨(Super PowerRail, SPR)架构,以进一步增强运算能力和能源效率。三星方面,其2nm开发代号SF2,据韩国消息来源指出试产良率高于预期,Exynos 2600处理器试产晶圆良率已达30%,若进展顺利,三星2nm可望在2025年第四季量产,与台积电N2几乎同期竞争。英特尔则制定雄心勃勃的制程路线图,计画在2024-2025年间连续推出Intel 20A(等效2nm)及18A(1.8nm)节点。尤其Intel 18A被视为其制程翻身的关键:英特尔于2025年初展示了首颗18A晶片「Panther Lake」,并宣布将于2025年下半年量产。 18A将采用RibbonFET(GAA晶体管)与PowerVia背面供电等新技术,预期大幅改善晶体管效能功耗比。不过,英特尔在先进制程商业化上仍面临不小挑战,包括良率爬升和产能争取等。

向1纳米迈进:在2nm世代之后,1.x纳米(即「埃级」Angstrom级)制程研发已在路上。全球主要代工厂的路线图显示,1nm左右技术可能于2027年至2030年间实现量产。台积电预计2nm之后持续缩小晶体管尺寸,结合新架构与新材料,保持摩尔定律延续;三星与英特尔也各自公布了朝1.4nm、1.8Å等节点挺进的蓝图。此外,业界探索的新晶体管技术包括堆叠式CFET(将N/P沟道晶体管垂直堆叠)以及2D半导体材料(如石墨烯、迁移率更高的双硒化钼等)有望在1nm以下时代派上用场,但在材料良率和制程整合方面仍有重大难题需克服。目前可以预见的是,进入次2纳米 领域后,研发成本与技术门槛极高,只有极少数厂商能够参与竞逐,全球晶圆代工的技术领先阵营可能进一步收敛。

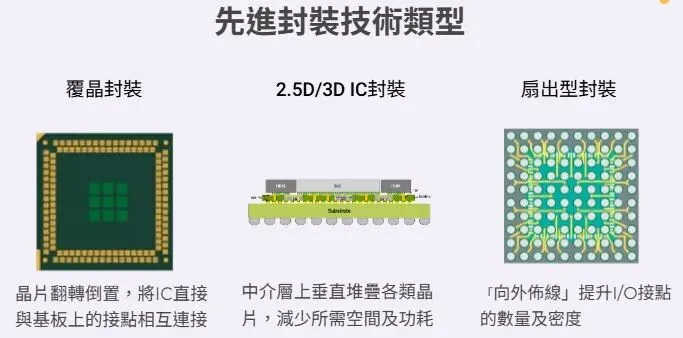

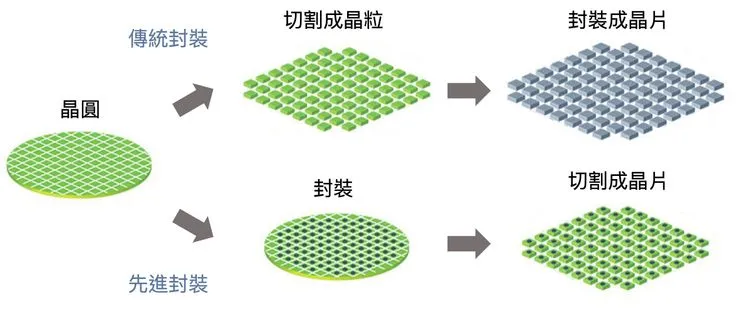

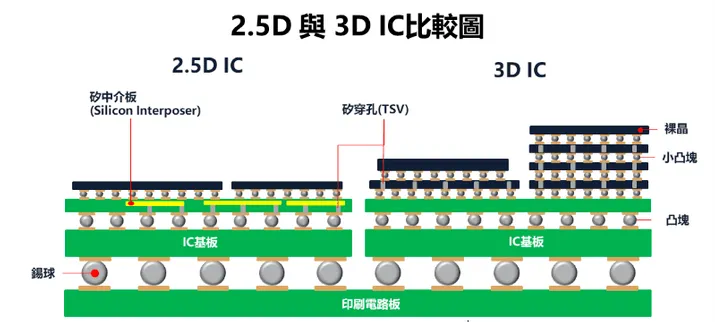

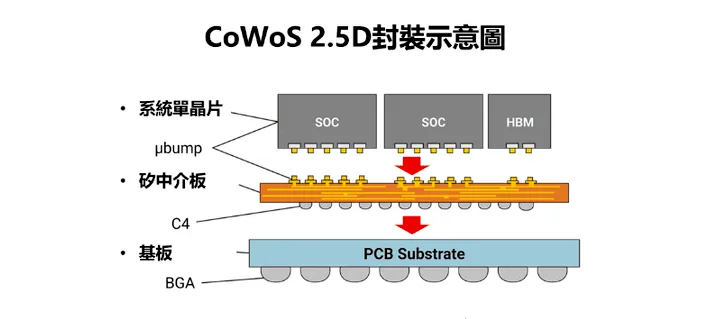

2.5D封装:所谓2.5D封装是指在封装基板与逻辑晶片之间加入一片高密度中介层(通常是矽中介层),将多颗晶片并排封装在该中介层上,再由中介层内部的通矽孔(TSV)实现晶片与基板间的垂直电气连接。这种方案保有平面布局的简单性(因此称为2.5D),又能利用矽中介层上细密布线实现晶片间高速互连。 2.5D封装的代表应用是将高频宽记忆体(HBM)与处理器并置于矽中介层上,例如台积电的CoWoS®(Chip-on-Wafer-on-Substrate)技术,可在单一封装中整合多颗GPU晶粒与多堆HBM记忆体。此类技术已被广泛应用于HPC加速卡与AI训练晶片中,如NVIDIA GPU透过CoWoS整合8颗HBM,使记忆体频宽大幅提升以满足AI模型训练需求。

3D封装:3D封装指垂直堆叠晶片的封装技术。透过TSV或先进混合键合(Hybrid Bonding)等手段,将两层或多层晶片直接堆叠在一起实现电互连。 3D封装可以进一步缩短晶片之间的讯号传输距离、提升密度并降低延迟,是目前先进封装的亮点之一。典型案例包括:逻辑晶片上堆叠高速缓存记忆体(如AMD的3D V-Cache技术,利用台积电SoIC实现CPU与SRAM快取裸晶的键合);处理器与HBM记忆体的立体集成(HBM本身也是DRAM晶粒的3D叠层);以及英特尔Foveros技术(在基底晶片上垂直整合小晶片,如Lakefield处理器将CPU逻辑层与I/O层堆叠)。 3D堆叠透过缩短晶片间连线,可显著降低讯号传输延迟与功耗,这对需即时处理庞大资料的AI/HPC晶片至关重要。此外,适度的3D堆叠有助于突破单一晶片尺寸受限于光罩(reticle)大小的瓶颈,透过拆分小晶片再堆叠来提高良率。

3.5D封装:所谓3.5D是一种融合2.5D与3D的混合封装架构,是在平面中介层整合与局部垂直堆叠之间取得折衷。具体而言,3.5D封装可以包含少量的垂直叠层(例如将小型的SRAM或快取晶片堆叠在大型处理器上)以及侧向的晶片并置(例如多颗逻辑晶片并排在中介层上),形成一个既有平面扩充又有局部3D堆叠的系统。这种架构的优点是在提升系统性能的同时,缓解纯3D封装的散热难题,因为并非所有晶片都叠在一起,高功率晶片仍可平铺降低热密度。例如,为了克服3D叠层的热限制,业界讨论将发热大的CPU/GPU与较不敏感的SRAM堆叠,而其他模组(如I/O或类比晶片)则放在中介层上。 3.5D因此提供了更灵活的晶片整合方式,被视为高效能封装的一个折衷路径,可同时兼顾性能、热管理与良率。

FOWLP与FOPLP:扇出型封装(Fan-Out)是另一类先进封装技术,不需要传统有机载板。 FOWLP(晶圆级扇出)将晶粒嵌入模塑料中,在重布层(RDL)上扇出形成引线;FOPLP(面板级扇出)则是在大型矩形面板上进行类似工艺。 Fan-Out封装的优点是省去封装基板,缩小体积且可以细化走线以提升I/O密度。早期FOWLP多用于手机射频模组、电源管理IC等小晶片,使封装厚度和成本下降。台积电的InFO技术(InFO-WLP)曾成功应用于苹果A系列手机处理器,提高了矽晶与封装的散热和电气性能。 FOPLP进一步将加工尺寸扩大到整块大面板,可一次布局更多晶片,理论上降低单位成本)。根据Yole的资料,面板级扇出相比晶圆级可节省20~30%成本,特别适合高产能应用。目前FOPLP已在中低阶手机、穿戴装置的封装上逐步采用。随着技术进步,业界也在尝试将Fan-Out用于更高性能需求的装置,以兼顾成本与性能:例如大型面板有望容纳AI加速晶片的扇出封装,以减少对矽中介层的依赖。不过,要实现这一点仍需克服翘曲变形、对位精度等挑战。值得注意的是,三大代工厂都不约而同投入面板级扇出研发:台积电据传正开发515×510 mm的大面板封装技术;三星与英特尔亦宣布在研,预示Fan-Out将成为下一个封装战场。

技术突破与应用场景:以上先进封装技术的发展,使得异质晶片整合成为可能。特别在AI和HPC领域,2.5D/3D封装已是高阶晶片的标配:例如每颗NVIDIA Hopper/Blackwell GPU均搭配多颗HBM记忆体透过矽中介层连接,以提供数TB/s等级的带宽。这类先进封装的需求暴增也反映在台积电的业务上——2024年台积电先进封装营收占比约8%,预计2025年将超过10%。尤其AI加速器对CoWoS等封装产能需求强劲,NVIDIA甚至预订了台积电2025年超过70%的CoWoS产能,用于其新一代GPU晶片封装。在行动装置领域,先进封装则强调轻薄与低功耗。 Fan-Out封装已广泛用于高阶手机射频前端和PMIC,以节省空间并提升性能。同时,新兴的晶片直结(Chiplet)设计也依赖先进封装实现,例如Apple M1 Ultra采用2.5D技术将两颗M1 Max裸晶并联互连,展现接近单颗巨型晶片的效能。总体而言,先进封装技术正快速成熟并多元化,从资料中心的AI加速卡到手机可穿戴装置,都出现对应的封装解决方案。可以预见,随着晶片功能整合度不断提高以及成本压力,封装将成为差异化竞争的关键,而不仅仅是传统制程尺度的竞赛。

异质整合的兴起:所谓异质整合(Heterogeneous Integration, HI),是指通过先进封装技术,将不同功能、不同材料或不同制程节点的晶片元件集成在同一封装中。与过去将所有功能模组设计在单一矽晶(SoC)的方式相比,异质整合允许晶片以「Chiplet晶粒」形式制造,再藉由2.5D/3D封装互连成一个完整系统。这种方法使各模组可以采用最适合的制程制造(例如高性能逻辑用先进节点,类比电路用成熟节点,记忆体用特殊工艺),然后在封装阶段组合,达成比传统SoC更高的良率和更低的成本。根据Semiconductor Engineering的分析,随着HPC需求提高,Chiplet和异质整合已成为关键解决方案,因其在提升良率、重复利用IP设计、增强性能以及优化成本等方面具有显著优势。简言之,异质整合为半导体产业提供了一条延续系统级进步的新途径,即使晶圆尺度微缩变慢,仍可藉由封装级创新持续提升系统效能。

对AI与HPC的影响:异质整合技术的成熟,对AI和HPC领域产生了革命性影响。首先,在性能与能效方面,将多颗晶片紧密互连可带来类似单晶的大带宽和低延迟。例如,高阶AI训练晶片往往需要与大量记忆体协同运作,透过2.5D/3D封装将HBM记忆体贴近运算晶片,可提供数百GB/s以上的存取带宽,同时大幅降低传输延迟,这对于加速深度学习模型训练至关重要。 NVIDIA近年AI GPU的卓越效能,正是仰赖台积电CoWoS技术把多堆HBM堆叠于GPU周围,异质封装功不可没。此外,在晶粒化设计下,HPC处理器可以拆解为数个小晶粒制造,再透过先进基板互连。例如AMD的EPYC伺服器处理器以多颗CPU小晶片(chiplets)组成,每颗chiplet都是完整的处理模组,透过矽基板(或有机载板上的高速介面)相连。这让AMD能以较成熟的14/7nm制程制造chiplet,以降低成本并提升良率,同时透过封装整合实现超过64核心的超大规模CPU,性能媲美单一巨大晶片。英特尔也采取类似策略,在Sapphire Rapids处理器中使用EMIB 2.5D桥接技术连接四颗处理晶片,未来的Ponte Vecchio GPU更是由数十颗chiplet构成的异质系统。

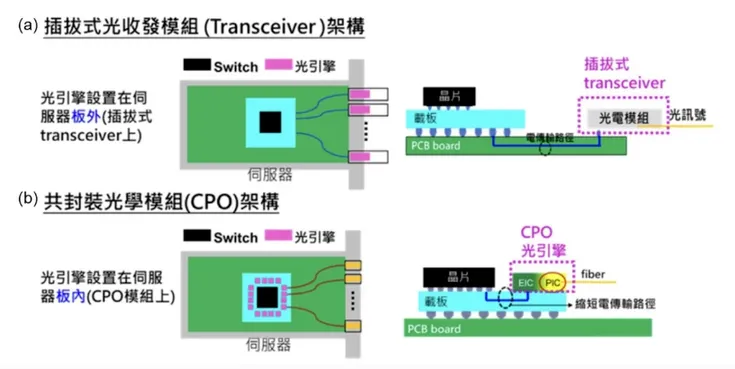

系统优势与新应用:透过异质整合,系统级性能可以超越传统单晶SoC的极限。一方面,提高良率降低成本:许多晶片分成小块制造,比起单颗大晶片更容易生产而不良率较低。另一方面,IP重用提升研发效率:厂商可以预先设计并验证好标准化的chiplet模组(如AI加速单元、IO介面单元等),在不同产品中重复组合使用,缩短开发时程。对AI而言,这意味着可以更快速地迭代硬体架构以适配新的演算法需求。例如,某AI加速器可藉由更换其中的存储chiplet或运算chiplet,迅速推出升级版本,无需从头重新设计整颗SoC。再者,异质整合还促进跨领域技术融合,如将光学元件与电子晶片封装在一起形成矽光子(Silicon Photonics)系统,用于高速光通讯连接AI数据中心。目前已有晶片将雷射光收发器与网路交换晶片以2.5D整合,达到每秒数百Tb的资料传输能力,被视为未来AI云端中共封装光学(CPO)的雏形。最后,异质整合对边缘AI与嵌入式HPC也带来影响。例如先进封装使得高性能AI晶片可以以模组化方式嵌入车用或物联网装置中,同时封装内集成异种感测器、记忆体,以满足即时运算需求。总的来说,异质整合已成为AI/HPC时代突破晶片性能天花板的关键技术之一,不仅提升了现有系统的效能功耗比,也开启了晶片设计与应用的新范式。

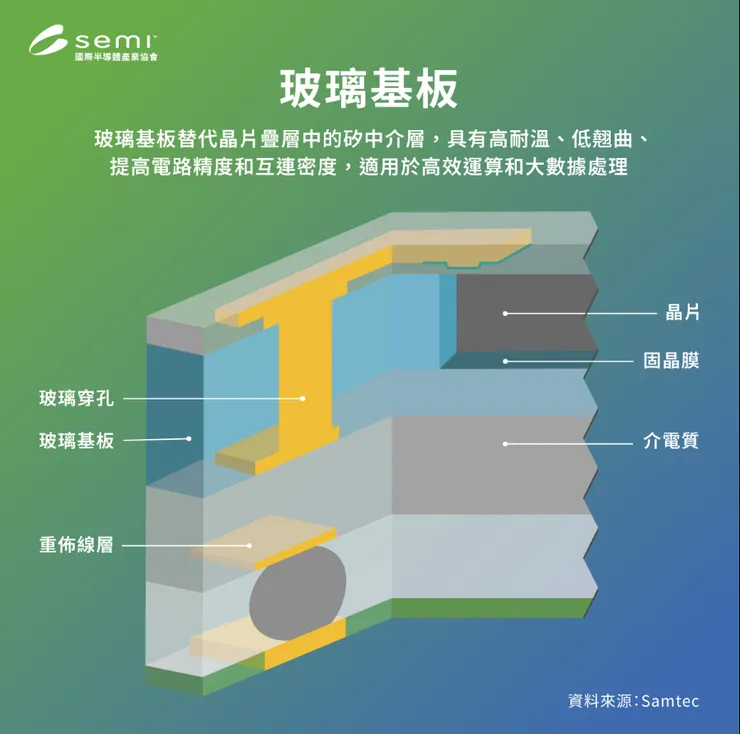

玻璃基板的崛起:在先进封装领域,「玻璃基板」被视为下一代关键材料,有望取代传统有机封装载板并克服矽中介层尺寸受限问题。玻璃材料具有多项优异特性:首先,玻璃的热膨胀系数接近矽,远低于有机材质,因而在高功耗晶片运作时更不易因热而翘曲变形,能提高封装的热稳定性。其次,玻璃具备低介电常数和低损耗优势,可减少高频讯号在走线中的延迟与串扰,提高讯号完整性。研究指出,在资料中心、电信和HPC等高速应用中,玻璃基板能显著提升系统效率和资料吞吐,并在RF射频领域因更佳阻抗控制而具吸引力。再次,玻璃基板可以采用大面板生产,突破目前12吋矽晶圆的尺寸限制。 Intel已展示约510×515mm的玻璃面板试产品,其面积超出12吋晶圆3倍以上。这意味单片玻璃可容纳更多晶片同时封装,提升生产效率并降低成本。然而,玻璃基板也面临挑战:材料本身脆性较高,超薄玻璃处理困难,且产业链需要开发通孔(TGV)制程、专用设备等配套技术。目前Intel率先投入玻璃基板研发,宣称将在2026-2030年实现业界首款玻璃基板量产应用,优先锁定资料中心AI加速卡和绘图GPU等高脚数、高频宽封装需求。台积电、三星、AMD等也不甘示弱,据报均启动相关布局。欣兴电子更与Intel深度合作,计画在2027年推动玻璃基板量产。可以预期,玻璃基板的导入将突破现有封装材料的性能天花板,为AI/HPC提供革命性的系统整合能力。

低介电材料与先进介电:半导体制程中,介电材料的创新对提升晶片速度同样重要。随着逻辑电路密度提升,布线间的电容效应导致RC延迟增加,因此各世代制程都引入更低介电系数(low-κ)的介电层来减少电容负载。从90奈米节点开始,业界采用SiO₂以外的低κ介电(如含碳掺杂的氧化矽),κ值从约4.0降至7nm时的~2.5,并在5nm以下尝试极低介电(ULK)材料甚至空气间隙技术,以继续降低介电常数。低κ材料虽能减RC延迟,但通常力学强度较弱,为维持晶圆良率需在材料结构与制程上加以平衡。同时,在先进封装中也出现了低损耗介电材料的需求。例如扇出型封装的重布层(RDL)介电,要求低介电损耗(Low Df)以保障高速讯号传输。材料厂商正研发新一代介电聚合物来提升RDL性能,如改良型树脂或封装级液态光阻,能在保持低κ的同时增强机械强度和热稳定。除此之外,用于高速封装基板的低诱电正切材料(如先进树脂、陶瓷填料)也在开发中,以降低高速IO走线的损耗。未来几年,从晶片内部互连到封装基板,介电材料创新将持续扮演提升讯号传输效能的关键角色。

低碳材料与永续制造:在追求性能之余,半导体产业亦肩负减碳与环保的责任。近年来各大晶圆代工与封装厂纷纷宣示碳中和目标(例如台积电承诺2050净零,并计画2040年达成100%再生能源电力),这也推动了相关低碳材料的快速发展。所谓低碳材料,指的是制造过程碳排放更低、可回收循环或替代高耗能原料的新材料。在半导体与电子领域,一些传统高污染、高耗能的材料正逐步被更环保的选项取代。例如,台湾厂商晶化科技开发出新型增层绝缘膜(TBF®)用于IC封装载板,其配方不需冷冻保存,仅需冷藏即可,降低制程能源消耗并减碳达50%。该公司亦引入溶剂回收系统、在地供应减少运输碳足迹、回收再利用包材等,以实现封装材料生产的永续化。又如日本DIC公司研发可回收的创新环氧树脂固化剂,在满足200°C以上耐热的同时,强调制程友好与材料可循环利用(有助封装废弃物的减量)。这些案例显示出材料供应链朝绿色配方、节能制程、本地化供应与循环经济的方向转型。未来,具有环保特性、低环境冲击的绿色半导体材料将成为市场新宠,既符应各国减碳政策,也将成为企业在低碳经济转型中的竞争优势。可以预见,「材料创新」与「永续发展」将双轮驱动晶圆代工产业的技术演进,在满足性能需求的同时达成环境友好。

台积电(TSMC) –技术领先者持续扩张:台积电作为全球晶圆代工龙头,持续引领先进制程与封装技术。市占率方面,2024年台积电占全球晶圆代工64.9%的份额,稳居第一。在先进制程布局上,台积电3nm已成功量产并获得主要客户(苹果、超微等)采用,2nm研发进展符合预期,将于2025年下半年量产。台积电2nm将采用GAA奈米片电晶体并优化布线与功率传输,提供较N3大幅提升的效能功耗表现。更长远地,台积电已启动1nm级别的前瞻研究(Ångstrom世代),确保在2030年前后仍保持技术领先)。除了晶圆制程,台积电也积极深耕先进封装。其推出的整合封装平台“3DFabric”,涵盖2.5D的CoWoS、InFO系列,以及3D的SoIC晶片堆叠技术,可提供从高性能到行动装置多样化的封装解决方案。特别是针对AI时代的需求,台积电大举扩充CoWoS产能:包括在台中、中科新建先进封装厂,并与日月光(ASE)、Amkor等合作提升产能,预计到2025年每月可提供7.5万片以上的CoWoS产能,比2024年翻倍。即使如此,市场对AI/HPC封装的需求仍有可能超出供给,台积电预计到2026年持续以50%以上年复合增长率扩张先进封装产能,以缓解供不应求。在全球布局方面,台积电也积极因应地缘需求:包括在美国亚利桑那兴建5nm/4nm晶圆厂,在日本熊本与Sony/DMG合作建12/16nm晶圆厂,并评估在德国建厂计画,以服务各地客户。不过,先进制程主要研发和产能仍集中在台湾本土,以维持技术密集产线的竞争力。总体而言,台积电未来计画聚焦在巩固先进制程龙头地位(持续技术演进并提高产能),以及打造完整半导体生态(从晶片设计支援到制造、封装一条龙),以保持对主要竞争者的领先优势。

三星电子(Samsung) –奋力直追的全方位竞争者:三星作为仅次于台积电的第二大晶圆代工业者,近年来加大投入试图缩小技术与市占差距。三星在先进制程上采取积极策略:2018年7nm率先引入EUV微影,2022年又全球首发3nm GAA晶体管,展现技术雄心。虽然初期在良率和量产时程上遭遇挑战,导致市占率一度从11.5%下滑至9.3%。但三星并未放缓脚步,目前5nm、4nm制程已获得高通、英伟达部分订单,3nm制程也正努力提升良率以吸引客户回流。展望2nm世代,三星宣称将在2025年底量产2nm GAA(SF2),并预计于2027年进一步推进到1.4nm节点。若2nm如期量产,三星有机会在先进技术时程上与台积电并驾齐驱。除了制程,三星利用自身IDM优势,在晶圆代工客户之外,还有自家Exynos行动SoC、影像感测器等产品可作为先进节点的试金石。在先进封装方面,三星近年建立了完整的技术组合。三星的I-Cube®方案(Interposer-Cube)对应2.5D矽中介层封装,已用于高带宽HBM与处理器的整合。 X-Cube®技术则是3D堆叠,可将SRAM等裸晶垂直叠放在逻辑晶片上,来提升缓存容量和性能。三星还提供2D封装(FOPKG)服务,以及针对手机、可穿戴装置的扇出型晶圆/面板级封装平台。三星深知仅凭制程不足以撼动台积电,因而强调提供代工+封装的一站式服务。在研发布局上,除了投入Panel Level封装外,三星也积极研发下一代基板技术。例如据报导三星亦着手玻璃基板试产,计画最快2025年下半年试产基板级SiP玻璃,以在新兴封装市场与英特尔竞争。整体而言,三星未来的策略是在制程技术上持续赶超(尤其GAA技术领先应用)、在先进封装上发挥IDM整合优势,并结合其存储器、面板等多元产业实力,打造差异化的代工服务。能否顺利提高良率、争取更多大客户,将决定三星在晶圆代工版图中的地位能否进一步提升。

英特尔(Intel) –重返先进制程与跨界代工:传统上英特尔以IDM模式自给自足,但近年在10nm/7nm工艺节点遭遇瓶颈,制程领先地位被台积电、三星超越。为此英特尔在2021年启动IDM 2.0转型,决定一方面加速追赶先进制程进度,另一方面成立英特尔代工服务(IFS)对外接单,成为晶圆代工市场的新竞争者。技术路线上,英特尔规划在2024-2025年间连发五个节点:Intel 7、Intel 4、Intel 3、20A、18A,誓言在2025年底重拾制程性能领先。眼下最受瞩目的是Intel 18A(相当于1.8纳米),该节点将运用RibbonFET全环绕栅和PowerVia背面供电等突破性技术,有望在单位面积性能上追上台积电2nm。 2025年初英特尔已成功展示18A试晶片并启动试产,宣称已有多家晶片设计公司参与测试。如果英特尔能按时量产18A并达到良率目标,将大大提高其代工业务的说服力。在先进封装与异质整合方面,英特尔其实一直走在前列。早在2018年英特尔就商用化了EMIB(嵌入式多晶片桥接)2.5D技术,用于Kaby Lake-G处理器将Intel CPU与AMD GPU相连。 2019年推出Foveros 3D封装,实现了业界首例异构晶片堆叠(Lakefield处理器),现在更发展出Foveros Omni和Direct等进阶版本,支援大规模chiplet整合。英特尔也积极研发玻璃基板并领先公布计画:将于2026~2028推出首款玻璃基板封装产品,以满足AI加速器和数据中心处理器对更大封装尺寸与更高I/O密度的需求。同时,IFS部门近年透过收购与合作扩充版图:如2022年收购Tower Semiconductor(以色列代工厂)计画虽告吹,但英特尔仍表明欢迎与外部合作开发特殊制程(如与联电共同研发12nm工艺)。整体来说,英特尔企图以「先进制程+ 先进封装」双管齐下重塑竞争力:不仅服务自身产品线(CPU、GPU、FPGA等)的需求,也希望吸引Fabless客户投单,成为媲美台积电、三星的第三大代工势力。未来挑战在于,英特尔能否一方面完成研发任务、另一方面建立客户信任,在剧烈竞争的代工市场占有一席之地。

其他主要代工业者:

联华电子(UMC):UMC近年选择不同于台积电的策略,专注于成熟及特殊制程而非追逐最先进节点。早在2018年,联电即宣布放弃自主14nm FinFET开发,转向专注12nm及以上节点的优化与特殊应用(如嵌入式快闪、射频、车用高压等)。目前UMC最先进量产节点为14nm,并无投入GAA晶体管研发计画。此策略使UMC避开了高昂的EUV设备投入与研发成本,在疫情晶片短缺期间凭借28nm等成熟工艺供不应求而获利大增。 UMC未来计画持续扩产22/28nm平台(在台湾与新加坡新建产能),并与英特尔等合作开发特殊制程IP,以巩固汽车、工业控制等市场。目前UMC虽无意涉足2nm以下战局,但稳定的良率和性价比使其在代工市场占有一席之地。

格罗方德(GlobalFoundries):格罗方德(下简称格方)原为AMD制造部门,近年同样调整定位至中端工艺供应商。格方在2018年放弃7nm FinFET开发,转而强化22FDX(22nm FD-SOI)、12nm等特色制程,以服务5G射频、物联网、车用晶片等领域。该公司在美欧亚多地布局生产基地(德国、美国、新加坡等),成为许多IDM和国防客户的成熟制程代工商。 2025年传出格芯有意并购联电的消息,若成真将打造一个成熟制程巨头,合并市占约可达全球成熟代工市场的28%。无论合并与否,格方未来重心仍将放在0.1µm~28nm范围内的技术优化与产能扩充,短期内不会重返先进节点研发,以错位竞争策略避开与台积电、三星正面交锋。

中芯国际(SMIC):近年受限于美国出口管制,无法取得EUV光刻机等关键设备,使其在7nm以下技术发展举步维艰。然而,中芯依然透过多重曝光技术研发出了接近7nm等级的制程,该报告指出该7nm样片与台积电7nm有相似之处,但推测为小规模验证性产出。此消息被视为中国半导体在逆境中的突破。不过,由于EUV受限,中芯的更先进节点(如5nm、3nm)短期难以实现。为弥补技术劣势,中芯正大举扩产成熟工艺,例如在北京、上海新建28nm及14nm产线。未来中芯将两条腿走路:一方面尽力在DUV范围内推进N+2代(约等7nm)工艺,另一方面拓展0.18µm~28nm产能满足汽车与工控市场需求。在地缘政治阴影下,中芯的技术提升将格外艰难,其走势亦牵动着中国半导体自给策略的成败。

日商Rapidus:这是一家日本政府主导的新创半导体公司,于2022年成立,目标是在日本重建先进逻辑制造能力。 Rapidus与IBM签订合作,获得IBM在实验室中开发的2nm技术授权(IBM曾于2021年展示全球首颗2nm晶片)。 Rapidus计画在2025年进行2nm试产,2027年实现量产,服务日本国内的先进晶片需求。目前Rapidus正于北海道建厂并培养技术团队,但要在短时间追上台积电/三星仍面临巨大挑战,包括人才、量产经验和生态系统等问题。不过,日本政府与企业(如丰田、索尼等都是股东)对其寄予厚望,期待未来能在特定高附加价值领域(车用AI晶片等)抢占一席之地。

日月光与安靠Amkor:除了晶圆制造,公司间的协同合作也是技术布局一环。全球封装测试龙头如日月光(ASE)与Amkor,近年加强与晶圆代工厂的合作,共同打造先进封装供应链。例如台积电为满足CoWoS急单,就委托部分制程给日月光协助,同时Amkor在美国亚利桑那兴建先进封装厂以配合Intel代工业务。这种垂直整合与策略联盟,使产业分工更紧密,技术研发与产能布局更具弹性。

台积电和日月光构筑的垂直供应链成为AI时代的关键支柱。三星和英特尔则投入巨资力图翻转局面,两者在先进技术和新材料上的竞争与合作(如共同推进面板级封装、各自研发玻璃基板)将决定未来市场格局。其他二线代工厂则精耕利基领域或成熟制程,成为主导厂的补充力量。可以预见,晶圆代工产业已从单纯的制程节点之争,演化为制程+封装+材料的全方位竞赛。在AI与HPC的驱动下,业者必须在多方面协调创新,方能在下一阶段的技术竞赛中胜出。

综上所述,晶圆代工产业正处于技术革新的关键时期。先进制程从3纳米向2纳米及以下迈进,在晶体管架构和微缩极限上持续突破;先进封装技术百花齐放,2.5D、3D、扇出封装等为晶片提供了新型态整合途径;异质整合打破传统SoC疆界,令系统性能随封装创新而节节提升;材料创新则为制程和封装提供支撑,玻璃基板、低κ介电、低碳材料等将成为下一代技术的基石。同时,全球主要业者各展所长,台积电巩固领先、三星英特尔奋起直追,其他代工与封装厂商也在新的细分市场寻求定位。在AI与HPC时代的浪潮下,晶圆代工产业的竞争与合作将更趋激烈且复杂。可以预见,唯有同时掌控制程、封装与材料三大关键技术,并灵活整合全球资源,才能在未来半导体版图中立于不败之地。

参考资料:

TrendForce研究,AI需求带动先进制程产能满载( [News] Two Contrasting Trends Emerge in Wafer Foundry Industry | TrendForce News )

TrendForce新闻,2奈米代工竞局与时程展望( [News] The 2nm Foundry Battle: TSMC Leads, Can Samsung and Intel Catch Up? | TrendForce News )

TrendForce新闻,台积电3奈米量产与2奈米进度( [News] The 2nm Foundry Battle: TSMC Leads, Can Samsung and Intel Catch Up?

SemiWiki分析,台积电2nm在IEDM 2024公布的性能数据( IEDM 2025 – TSMC 2nm Process Disclosure – How Does it... - SemiWiki )。

TrendForce新闻,三星3nm GAA量产与2nm研发良率( [News] The 2nm Foundry Battle: TSMC Leads, Can Samsung and Intel Catch Up? | TrendForce News )

TrendForce新闻,英特尔18A进展与量产计画( [News] The 2nm Foundry Battle: TSMC Leads, Can Samsung and Intel Catch Up?

TrendForce新闻,晶圆代工先进与成熟制程市况( [News] Two Contrasting Trends Emerge in Wafer Foundry Industry | TrendForce News )

Semiconductor Engineering,3.5D封装概念与优势解析( 3.5D: The Great Compromise )

Semiconductor Engineering,异质整合提升HPC性能与良率( Heterogeneous Integration Semiconductor Engineering )。

TrendForce新闻,CoWoS封装因AI需求供不应求,台积电积极扩产( [News] TSMC Set to Expand CoWoS Capacity to Record 75,000 Wafers in 2025, Doubling 2024 Output

TrendForce新闻,NVIDIA预订台积电2025年超过70% CoWoS产能( [News] TSMC Reportedly Sees CoWoS Order Surge, with NVIDIA Securing 70% of 2025 CoWoS-L Capacity

SemiEngineering专栏,Chiplet与异质整合成为HPC关键解决方案( Heterogeneous Integration Semiconductor Engineering )。

Asia Times报导,中芯国际成功试产7奈米晶片之解析( SMIC's 7-nm chip process a wake-up call for US - Asia Times )

WallstreetCN技术专栏,玻璃基板在先进封装中的优势与挑战(玻璃基板之争) (玻璃基板之争)。

TrendForce新闻,晶圆代工大厂竞逐面板级扇出与玻璃基板技术( [News] New Battleground for TSMC, Samsung & Intel in Panel-Level Packaging | TrendForce News )

工研院产业报告,先进封装发展与低碳材料趋势(先进半导体封装与低碳材料发展趋势.pdf ) (先进半导体封装与低碳材料发展趋势.pdf )。

TechPowerUp新闻,格罗方德拟并购联电强化成熟制程版图( GlobalFoundries Explores UMC Merger to Strengthen Mature Node Manufacturing | TechPowerUp )

晶圆厂系列|Mordor Intelligence :半导体代工市场规模及份额分析 (2025-2030 年)

晶圆厂系列|集微咨询发布《2025中国晶圆代工行业上市公司研究报告》

晶圆厂系列|2025年全球晶圆产能情况,及欧、日、韩、及东南亚等地最新晶圆厂分布