引言

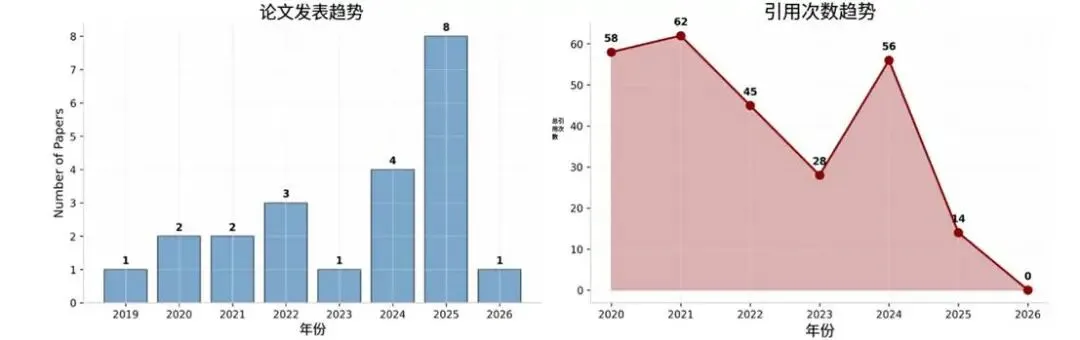

本报告基于对台积电TSMC及相关研究团队2019至2025年间发表的液冷相关学术论文的系统梳理,解析了台积电在芯片液冷领域的技术演进轨迹与体系化布局。研究表明,台积电已形成从基础封装工艺到系统级集成的完整热管理技术体系,涵盖微通道液冷、直接芯片冷却及SoIC®系列等技术路线。

01

技术演进总览:从远端辅助到原生集成

台积电芯片液冷技术的演进本质是散热单元与计算单元空间关系的重构。传统散热将芯片视为热源、液冷作为外部辅助手段;而台积电通过将冷却结构嵌入芯片内部与封装层级,使热管理成为芯片架构的原生属性。

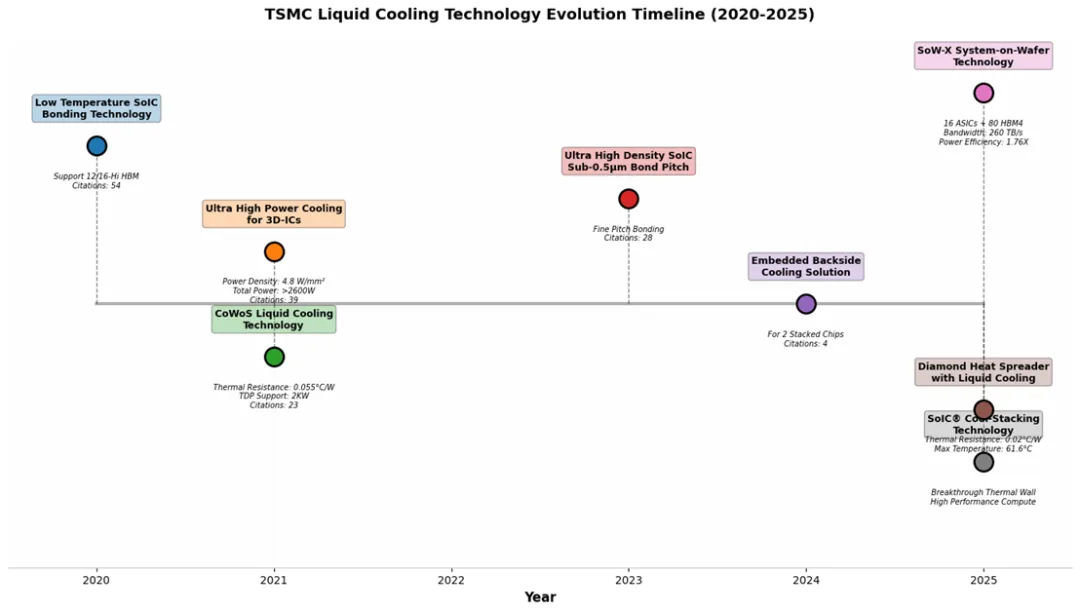

图1:台积电及相关研究团队液冷技术研究(2020-2025年)

这一演进呈现三条清晰技术脉络。

其一,空间维度的内嵌化:冷却单元从机柜级向封装级、芯片级、晶圆级逐步内移,热阻指标从0.064°C/W降至0.02°C/W,降幅达69%。

其二,系统维度的整合化:从单芯片独立散热发展到多芯片协同冷却,再到整晶圆热管理,散热功率从单芯片2600W扩展到整晶圆级数十千瓦规模。

其三,工艺维度的晶圆化:从后段组装工艺发展为前段晶圆级工艺,并与3nm制程实现协同,标志着液冷技术深度融入半导体制造主流程。

图2:台积电液冷研究方向分布图

02

空间维度演进:冷却边界的逐层内移

2.1 封装级突破:CoWoS平台液冷工业化

2021年是台积电液冷技术工业化的关键节点。当年发表的学术论文展示了业界首个基于CoWoS平台(Chip on Wafer on Substrate)的先进液冷技术,该技术针对2.5D封装架构优化,支持高达2KW的热设计功耗。

研究团队开发了带盖液冷与直接液冷两种技术变体。

测试数据显示,带盖方案结到流体热阻仅为0.064°C/W,而直接液冷方案在流速40 ml/s条件下进一步优化至0.055°C/W。该研究建立了完整的有限元分析模型,为后续产业化提供了仿真方法论。

这一技术确立了CoWoS液冷作为HPC芯片标准散热方案的行业地位,为NVIDIA A100及H100等产品的散热设计提供了原始技术原型。

2.2 芯片级直接冷却:热阻数量级降低

同期实现突破的芯片级直接冷却技术采用熔融键合硅盖结构(fusion bonded silicon lid),在硅盖内部制造沟槽与网格冷却结构,使冷却水直接流经逻辑芯片背面。该技术实现了功率密度4.8 W/mm²的突破,单芯片散热功率超过2600W,热阻降至0.02°C/W以下,较传统风冷方案实现数量级提升。

这一突破证明了冷却结构可作为芯片架构的原生属性而非外部附加,引导行业从封装散热向芯片散热范式转移,为后续Blackwell等千瓦级AI芯片的散热奠定了技术基础。

2.3 立体散热架构:3D IC嵌入式背面冷却

面对3D IC堆叠架构的散热挑战,2024年学术界发表的学术论文提出了嵌入式背面液冷方案,专门针对双芯片堆叠架构优化。技术核心在于将微流道直接集成在芯片背面,冷却液流经芯片背部微通道直接带走热量,从而消除了热量向下层芯片的传递路径,实现多芯片协同冷却的立体散热架构。

该技术使3D IC不再受限于热堆积瓶颈,为高带宽存储器与逻辑芯片的垂直整合提供了热管理保障,支撑了后续超高密度集成方案的技术实现。

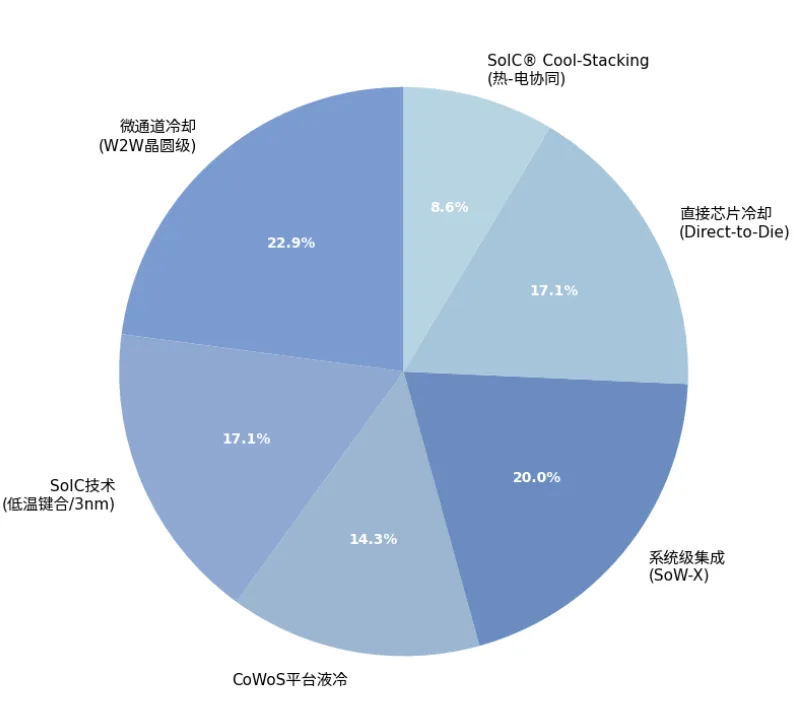

2.4 晶圆级热管理:散热面积的指数级扩展

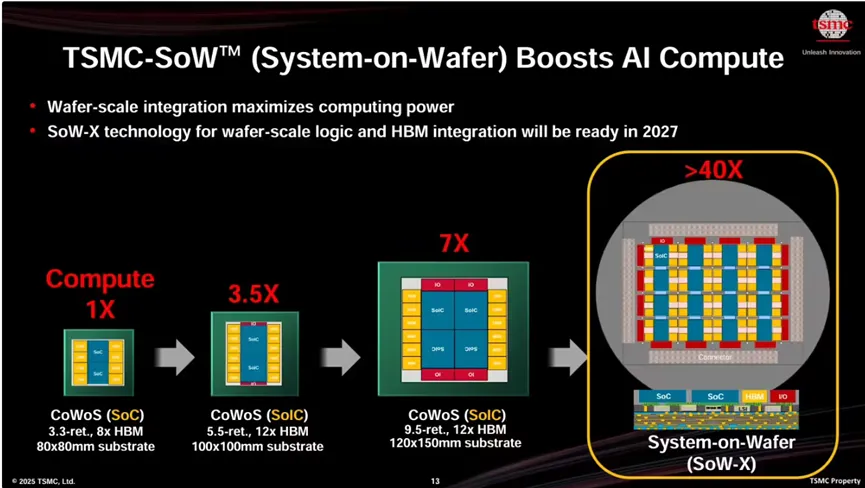

2025年提出的SoW-X技术(System-on-Wafer-X)代表了空间维度的终极扩展。该技术在单个晶圆上集成16个全光罩尺寸ASIC、80个HBM4模块以及2800个224Gb/s长距离SerDes通道,通过晶圆级液冷实现整片晶圆的统一热管理。

图3:台积电SoW-X技术

相比传统单芯片封装后独立散热的模式,晶圆级冷却将散热面积从平方毫米级芯片扩展到平方分米级整晶圆,通过整体流场设计实现热量的全局均衡。系统仿真表明,该技术在260TB/s芯片间带宽和80TB/s外部带宽的高功率场景下,仍能保持可控的热条件,系统功耗降低17%,性能提升46%,能效比提升1.76倍。

晶圆级微通道工艺采用8英寸W2W(Wafer-to-Wafer)低温Cu-Cu键合工艺,实现微通道晶圆与CMOS晶圆的一体化集成。其关键产业化突破在于兼容标准FC(Flip-Chip)封装工艺,使液冷结构能在现有产线中直接制造,无需额外后段工序,标志着液冷从单芯片后段组装转向整晶圆前段集成。

03

系统集成演进:从单点优化到协同架构

3.1 异构集成基础:SoIC键合技术体系

2020年发表的学术论文奠定了低温SoIC键合工艺基础(System on Integrated Chips),该技术支持12至16层高带宽存储器堆叠,为后续液冷技术提供了封装结构基础。其低温键合特性确保微通道与芯片连接的可靠性,该研究在学术界获得54次引用,成为该领域奠基之作。

后续发展的SoIC技术实现了3μm间距的低温SoIC方案,针对HPC应用优化电气和热性能,并集成热传感器阵列进行实时温度监控,标志着从被动散热向主动热管理的演进。进一步的研究实现了亚0.5μm键合间距,为液冷技术提供了更精细的集成基础,使冷却结构与芯片电路的协同设计成为可能。

3.2 下一代平台:3nm节点SoIC集成

2024年的研究将SoIC技术与台积电3nm制程结合,支持超高带宽HPC应用。该技术展示了液冷与最先进制程节点的协同能力,证明热管理结构可与晶体管微缩同步发展,为摩尔定律的延续提供了热管理基础。

3.3 热-电协同设计:SoIC® Cool-Stacking

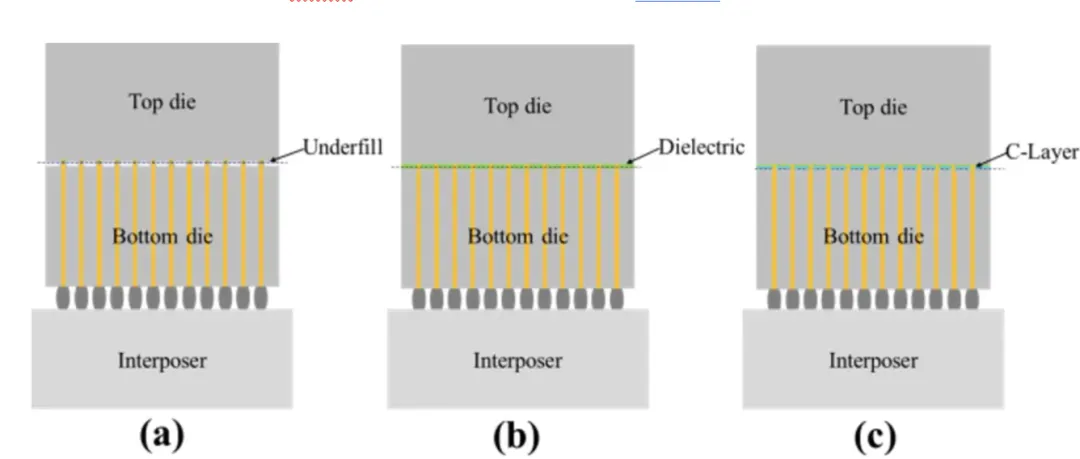

2025年提出的SoIC® Cool-Stacking(SoIC-CS)技术代表了热管理与电路设计的深度协同。关键创新在于用称为C层的专用高导热材料替换传统的导热性能不佳的介电层。该技术针对AI系统在高性能计算数据中心面临的散热挑战,将冷却结构作为堆叠架构的有机组成部分,在SoIC平台上实现电气互连与热管理的双重集成。

图4:(a)微凸点、(b)标准SoIC和(c)SoIC-CS键合方案之间的结构差异,显示C层集成如何优化热传导路径。

该技术突破了传统先电气设计、后热管理补救的串行模式,实现并行协同设计,突破了传统热管理的技术瓶颈,实现高功率热管理和能效优化的统一,使3D IC架构不再受限于热墙约束。

04

产业生态内材料与工艺创新探索

4.1 金刚石散热片集成:材料体系的革新

2025年学术界发表的学术论文提出了集成金刚石散热片液冷方案(Integrated Diamond Heat Spreader),将微流道直接嵌入顶部金刚石散热片中,结合金刚石超高导热系数约2000 W/m·K和主动液冷的优势。在2000W负载条件下,结到流体热阻仅为0.02°C/W,最大结温控制在61.6°C,相比被动金刚石散热片方案总热阻降低50%。

该技术将被动散热材料转化为可量产的主动散热组件,通过系统仿真优化微通道几何结构,采用更多数量、更窄宽度的流道设计,有效缓解热点形成,提升温度均匀性,为超高功率AI芯片提供了可量产的解决方案。

4.2 微射流阵列:直接冷却的精细化变体

同期学术界提出的微射流阵列(Micro-Jet Array)直接液冷技术通过微射流阵列将冷却液直接喷射到芯片表面,实现更高效的局部冷却。作为直接水冷技术的精细化发展,该技术针对高性能计算芯片的局部热点进行强化冷却,代表了直接冷却技术的演进方向。这两个创新探索,均是产业生态内以台积电为基准的第三方研究成果。

05

产业化路径总结

基于技术演进脉络,台积电芯片液冷技术的产业化呈现清晰的三阶段路径。

第一阶段为2020至2021年的技术验证与标准确立期。该阶段建立低温键合基础工艺,确立CoWoS液冷工业标准,热阻指标达到0.055至0.064°C/W水平,验证芯片级直接冷却可行性,功率密度达到4.8 W/mm²,单芯片散热能力突破2600W。此阶段完成从实验室原理验证到工程样机测试的跨越,确立技术可行性。

第二阶段为2022至2024年的异构集成与立体散热期。该阶段实现热-电协同监控,完成3D IC立体散热与3nm制程协同验证。此阶段完成与先进封装流程的深度整合,实现工程化验证与工艺兼容性确认。

第三阶段为2025年起的晶圆级量产与材料创新期。该阶段实现8英寸晶圆级微通道集成,兼容标准FC工艺,实现SoIC® Cool-Stacking热墙突破,,整晶圆级热管理SoW-X技术实现能效提升1.76倍。此阶段完成产业化验证,具备支撑全球AI算力基础设施的量产条件。

图5:台积电液冷技术演进时间线

06

结论

台积电的技术路线标志着芯片热管理正经历从"外部辅助"到"内部原生"的范式转移。当液冷从机房级工程方案演进为晶圆级制造工艺,散热能力不再仅仅是芯片设计的后置约束,而是与晶体管密度、互连带宽并列的核心性能指标。

这种"热-算协同"的架构思维,正在重塑高性能芯片的设计边界,使得持续突破功耗墙成为可能。随着晶圆级液冷技术进入量产阶段,全球算力基础设施的技术基座正在发生结构性变化,从传统的风冷架构向液冷原生架构演进,为下一代AI芯片的规模化部署提供了关键的技术支撑。

声明:本文部分内容来源于公开资料整理,相关版权归原作者所有,若涉及版权或其他问题,请及时与我们联系处理。欢迎行业同仁投稿交流,共同推动技术进步!

我们汇聚了一群“算力冷时代”有识之士,特别打造了 “大咖谈”、“冷洞见”、“拆技术”三大专栏,旨在从不同维度深度剖析算力与冷却、人工智能与未来能源产业的要点、趋势和产业机会,让每个人都能从中获得有价值的知识、启发和产业机会。关注我们的公众号,一起开启思想的碰撞与融合,推动技术突破与创新吧!