第一章 互联技术的巅峰:PCIe 8.0与448 Gbps SerDes的演进

互联技术在2026年已正式进入“超高速时代”。PCIe 7.0规范的逐步成熟与PCIe 8.0路径规划的提前开启,标志着I/O带宽每三年翻倍的定律在AI集群的压力下不仅得以维持,甚至在研发节奏上有所加速 。

1.1 PCIe 8.0:迈向1 TB/s 双向带宽的征程

在DesignCon 2026的展厅中,Marvell展示了运行在256 GT/s数据速率下的PCIe 8.0 SerDes原型,这一动作比标准的最终定稿(预计为2028年)提前了近两年 。这种“前瞻性演示”旨在为超大规模云服务商提供路径规划依据,使其能够在基础设施架构层面提前布局,以应对未来十年内AI工作负载对带宽的极端需求 。

PCIe 8.0的技术挑战在于物理层(PHY)如何在极高的频率下维持信号完整性。在256 GT/s的速率下,传统的铜缆互连面临着严重的损耗挑战,业界开始通过低功耗、低延迟、低误码率(BER)的重定时器(Retimer)和有源电缆(AEC)技术来扩展传输距离 。

| 技术特性 | PCIe 6.0 | PCIe 7.0 | PCIe 8.0 (预研) |

| 最大数据速率 (GT/s) | 64 | 128 | 256 |

| x16链路双向带宽 (GB/s) | 256 | 512 | 1024 (1 TB/s) |

| 调制方式 | PAM4 | PAM4 | PAM4 / 高阶调制探讨 |

| 预计标准定稿时间 | 2022 | 2025 | 2028 |

| 核心应用场景 | 企业级计算 | 800G 网络/AI 初级集群 | 兆瓦级 AI 数据中心/自动驾驶云 |

数据分析指出,PCIe 8.0的演进不仅仅是速度的提升,更是对链路可靠性的重新定义。Marvell的演示中采用了TE Connectivity的AdrenaLINE Catapult连接器,通过优化的铜缆和光学通道,实现了在极低功耗下的高性能传输 。

1.2 448 Gbps SerDes:跨越112 GHz 奈奎斯特频率的障碍

如果说PCIe 8.0代表了工业标准的上限,那么224 Gbps向448 Gbps的跨越则代表了物理工程的极限挑战 。Samtec在大会上深入探讨了448 Gbps PAM4信号的恢复问题。当数据速率翻倍至448 Gbps时,奈奎斯特频率随之翻倍至112 GHz,这意味着通道中的寄生效应、通孔残桩(Via Stubs)以及介质损耗将成为设计中的统治性因素 。

根据香农定理(Shannon's Law),要在有限带宽内提升数据速率 $R$,必须在信噪比(S/N)与编码效率之间寻求精细平衡。

$$C = B \log_2(1 + \frac{S}{N})$$

在112 GHz的频率下,频谱显示出严重的滚降(Roll-off)和共振。业界目前倾向于继续在448 Gbps中使用PAM4调制,以保持与现有800G/1.6T光学模块的向后兼容性,并利用其成熟的测试设备生态系统 。然而,为了应对损耗,必须引入复杂的次奈奎斯特均衡(Sub-Nyquist Equalization)技术来优化频谱效率 。

1.3 高阶调制与前向纠错(FEC)的博弈

随着速率提升,误码率的控制变得愈发复杂。在448 Gbps路径规划中,关于是否引入PAM6或PAM8调制的讨论非常热烈 。虽然高阶调制可以降低符号速率,但其对电压噪声容限的要求也呈指数级上升。当前的共识是,为了满足AI/ML对延迟的高度敏感,必须开发更低延迟、更强纠错能力的FEC算法 。

第二章 智能体AI:电子设计自动化的范式转移

DesignCon 2026最显著的趋势之一是AI从“辅助工具”进化为“自治智能体(Agentic AI)”。Mark Ren在主题演讲中详细阐述了这一转变:从最初只能修复简单的RTL语法错误的单一代理,进化到能够直接从规范生成完整RTL设计的跨领域多智能体系统 。

2.1 芯片设计中的“设计智能体”

Cadence推出的ChipStack AI Super Agent代表了这一领域的技术前沿。它不仅是一个优化引擎,更是一个具备推理、目标分解和多步工作流执行能力的系统 。这种智能体能够:

自动分解任务:将复杂的验证目标分解为可执行的子任务。

上下文关联:实时理解设计文件、测试平台与原始规范之间的复杂逻辑关系。

自适应策略:根据仿真结果动态调整交叉运行策略,从而将验证效率提升5到10倍 。

2.2 验证瓶颈的突破:调试智能体

在现代芯片开发中,验证往往占据70%以上的周期。DesignCon 2026展示的“调试智能体(Debug Agent)”能够通过智能关联波形数据、断言记录和日志文件,自动识别可疑的信号跳变,并生成针对性的调试场景供工程师审核 。这种从被动检索到主动推理的跨越,极大地减轻了工程团队的负担,使他们能够从低价值的重复任务中解放出来,专注于高层架构设计 。

| 智能体类型 | 核心功能 | 对设计周期的影响 |

| RTL 代码智能体 | 从自然语言生成综合后的 RTL;检测编码违规 | 缩短 RTL 编写周期 40%;显著提升代码质量 |

| 跨时钟域 (CDC) 智能体 | 自动配置并运行 CDC 验证;提供基于 AI 的设计修正 | 消除由于异步设计导致的流片风险 |

| 验证规划智能体 | 分析设计规范,自动生成全面的验证计划 | 确保测试覆盖率无死角 |

这种基于AI的设计流程不再局限于特定的模型。Siemens的Questa One工具套件采用了框架无关的架构,集成了NVIDIA Llama Nemotron等多种大语言模型(LLM),确保了设计的安全性与灵活性 。

第三章 先进封装与材料创新:打破摩尔定律的束缚

当单体芯片尺寸逼近光刻掩模版极限(Reticle Limit),且最新工艺节点的成本呈指数级增长时,芯粒(Chiplet)和3D-IC架构成为了维持性能增长的唯一路径 。

3.1 芯粒架构与UCIe标准的普及

在DesignCon 2026上,芯粒互连标准(UCIe)已成为跨厂商协作的基石。Intel展示了代号为“Pike Creek”的测试芯片,该芯片通过EMIB先进封装技术,成功连接了基于Intel 3工艺的芯粒与基于TSMC N3E工艺的Synopsys芯粒 。这种异构集成(Heterogeneous Integration)的优势在于:

良率优化:更小的芯片单元意味着更高的制造良率。

成本缩减:计算核心可采用5nm/3nm顶级工艺,而I/O和内存控制器则可采用更成熟、成本更低的工艺 。

灵活性提升:实现类似“积木式”的芯片开发,大幅缩短上市时间 。

3.2 玻璃基板:封装材料的革命

Intel在大会上宣布的玻璃基板(Glass Substrates)技术被视为本世纪下半叶封装领域的最大跨越 。相比传统的有机基板,玻璃具有卓越的物理特性:

极高的互连密度:Intel预计玻璃基板可实现10倍的互连密度提升,支持到2030年在一个封装内集成1万亿个晶体管的目标 。

尺寸稳定性:在高温环境下,玻璃的变形极小,这对于需要精准对齐的超大封装至关重要。

嵌入式无源组件:玻璃基板允许直接在材料内部嵌入电感和电容,显著改善电源完整性并缩减封装尺寸 。

玻璃基板最初将应用于对带宽和散热要求极高的数据中心、AI加速器以及高性能图形芯片中 。

3.3 3D-IC中的热管理挑战

多层芯粒堆叠虽然提升了晶体管密度,但也带来了严重的散热问题。单封装功耗现在已攀升至数百瓦,甚至上千瓦。DesignCon 2026的多个分论坛讨论了微通道液冷(Micro-channel Liquid Cooling)和架构-冷却协同设计(Architecture-Cooling Co-design)的重要性 。通过在封装设计阶段就引入热仿真,工程师可以识别出局部热点(Hotspots),并通过优化芯粒排列和热界面材料(TIM)来缓解散热压力 。

第四章 电源完整性与AI时代的散热困局

人工智能不仅仅是对信号速度的考验,更是对电力系统和热管理极限的挑战。随着NVIDIA等公司最新的GPU功耗达到1400W,传统的板级电源分配已无法满足需求 。

4.1 垂直电源分配(Vertical Power Delivery)

为了应对极高的电流密度和瞬态响应要求,垂直电源分配正成为主流趋势。通过从封装底部垂直输送电流,可以显著缩短传输路径,降低IR压降,并为顶部的高速I/O留出更多走线空间 。Empower Semiconductor在会上展示了其嵌入式硅电容(ECAP)组合,这些电容具有极低的等效串联电感(ESL),能够直接集成到处理器基板中,为极速切换的AI内核提供稳定的电能缓冲 。

4.2 800V机架系统与GaN的应用

在数据中心层面,电源架构正在向800V系统转型,以支持兆瓦级的服务器机架 。氮化镓(GaN)半导体因其高压下的高速切换能力,成为新一代机架电源的核心技术。GaN不仅能提升电源转换效率,还能缩小电源模块体积,这在空间受限的数据中心环境中至关重要 。

| 电源技术演进 | 传统架构 | AI 时代架构 |

| 输入电压 (机架级) | 48V | 800V |

| 功率转换器件 | Si MOSFET | GaN / SiC |

| 电容部署位置 | 板载 | 嵌入式基板 (ECAP) |

| 散热方式 | 风冷 | 液冷 (冷板/浸没) |

第五章 信号完整性工程的基石:Bert Simonovich与其贡献

信号完整性(SI)专家Bert Simonovich在DesignCon 2026上被授予“年度工程师”称号。这一荣誉不仅是对他50年职业生涯的肯定,更是对他开发的“Cannonball”导体粗糙度模型的致敬 。

5.1 Cannonball 模型的物理意义

随着信号频率上升,电流趋肤效应(Skin Effect)导致电流主要在导体表面流动。此时,导体的微观表面粗糙度会显著增加信号的损耗和衰减。Simonovich开发的Cannonball模型是Huray模型的简化且更实用的版本,它允许设计工程师仅根据PCB材料商提供的数据表参数(如Rz粗糙度)即可准确预测传输线损耗,而无需进行复杂的实验拟合 。

这一模型的物理基础在于将表面粗糙度抽象为紧密堆积的小球(类似炮弹堆放),从而计算出导体的有效电阻增加系数。它已被主流EDA工具集成,成为112G和224G设计的标准建模手段 。

5.2 职业生涯与工程传承

Simonovich从电信行业的T1线路起步,见证了背板技术从非接触式互连向如今每秒数百Gb速率的跨越 。他特别强调了导师制的重要性,在担任DesignCon技术委员会成员期间,他致力于指导第一批论文作者,确保SI/PI领域的知识体系能够代代相传 。

第六章 测试与测量:赋能3.2T信号完整性

在极高频率下,验证设计的准确性需要前所未有的带宽和精度。DesignCon 2026展示了多款支持高达250 GHz频率的测试系统 。

6.1 250 GHz 网络分析系统

Keysight展示了其物理层测试系统(PLTS2026),该系统结合了NA5307A频率扩展器,能够覆盖高达250 GHz的带宽。这对于表征1.6T互连以及早期的3.2T路径规划至关重要 。在100 GHz以上的频段,任何微小的几何误差都会导致显著的反射,这种高带宽测量能力是验证新一代芯片组和PCB材料的基础。

6.2 自动化多端口 S 参数测量

随着AI集群中互连通道数量的激增,手动测试已不再可行。Anritsu展示了集成了ATS自动化软件的ShockLine VNA解决方案,配合可扩展的多端口RF开关矩阵,能够实现对AI/数据中心背板及服务器电缆的端到端、无干预表征 。这种自动化流程不仅极大地提升了测试效率,更通过消除人为操作误差提高了数据的重复性 。

| 测试项目 | 核心设备 | 技术指标 |

| 1.6T/3.2T 互连表征 | Keysight PLTS2026 + NA5307A | 250 GHz 带宽 |

| 高速 SerDes 误码率分析 | Anritsu MP1900A | 64 Gbaud PAM4 / 128 GT/s |

| 内存合规性测试 (GDDR7) | Keysight SNDR 测量套件 | 支持 PAM3 调制调试 |

| 电源轨噪声测量 | Picotest 2000 Amp 模拟系统 | 支持超大核心电流分析 |

第七章 展望未来:量子计算、空间科学与硅经济的终局

DesignCon 2026的视野不仅局限于当前的商业应用,更投向了量子互连和星际探索的远景。

7.1 量子互联网:从“幽灵作用”到超高速公路

Joseph Lukens教授在主题演讲中描绘了基于纠缠态的量子互联网 。量子互连面临的挑战不仅是极低温度的环境需求,更是如何将脆弱的量子态传输与现有的光纤和电子基础设施相结合。虽然目前仍处于纠缠测试床的实验阶段,但量子密钥分发(QKD)等商业化应用的成熟,正在为未来的“量子信息超高速公路”奠定基础 。

7.2 空间电子学:NASA的科学目标

NASA的Bhanu Sood阐述了高级电子设计在月球、火星及更远深空任务中的核心作用 。空间环境对电子系统的要求极为苛刻:

抗辐射设计:在不牺牲计算性能的前提下,确保高集成度芯片在强宇宙射线下的可靠性。

微型化传感:开发集成光子系统,以实现更轻、更高效的行星探测载荷 。

自主导航:高性能板载计算能力是实现可持续月球运行和火星着陆的关键。

7.3 全球供应链与宏观趋势

尽管技术创新突飞猛进,但行业仍面临关税、供应链不稳定以及人才短缺等外部挑战 。半导体行业正在通过“AI驱动的工厂”和“端到端数字孪生”技术来增强韧性,以期在2026年达到全球晶圆代工市场约2190亿美元的新高峰 。

结论

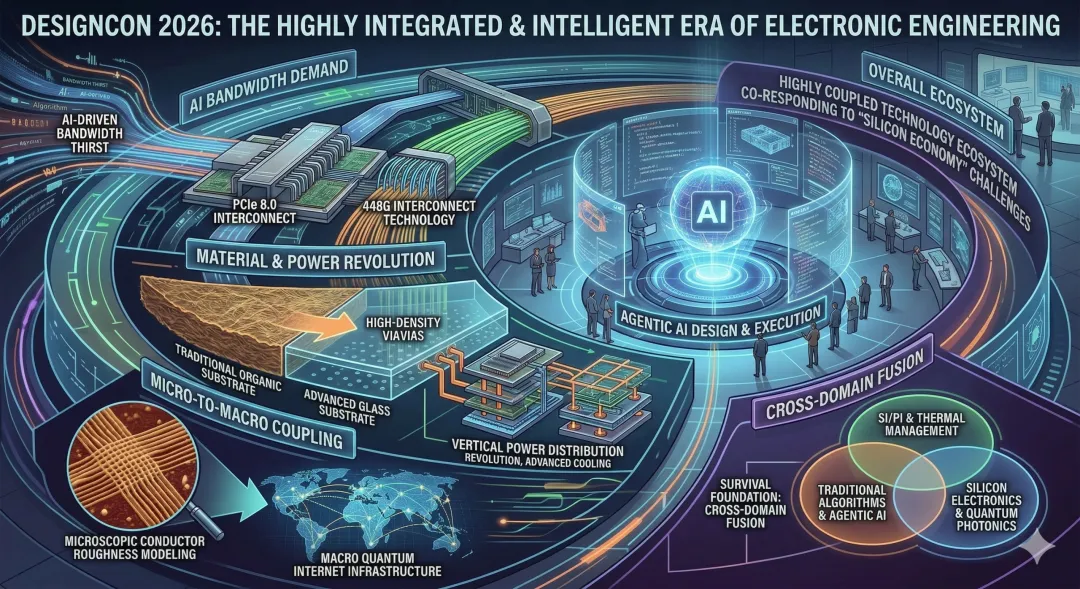

DesignCon 2026标志着电子工程进入了一个全新的高度集成化和智能化时代。我们观察到的核心逻辑如下:AI负载对带宽的渴求直接推动了PCIe 8.0和448G互连的技术攻关;互连速率的提升又反过来迫使材料科学从有机基板转向玻璃基板,并要求电源分配系统进行垂直化革命。在这一切复杂性之上,智能体AI正逐步接管设计的具体执行工作,重新定义了人机协作的工程范式。

从微观的导体粗糙度建模到宏观的量子互联网建设,DesignCon 2026不仅展示了单个节点的进步,更展示了一个高度耦合的技术生态系统如何共同应对“硅经济”时代的终极挑战。对于专业工程师而言,跨领域的知识融合——SI/PI与热管理、传统算法与代理AI、硅基电子与量子光子——已不再是可选项,而是生存的基石。