1.台积电业绩分析—业绩暴增的深层次原因挖掘

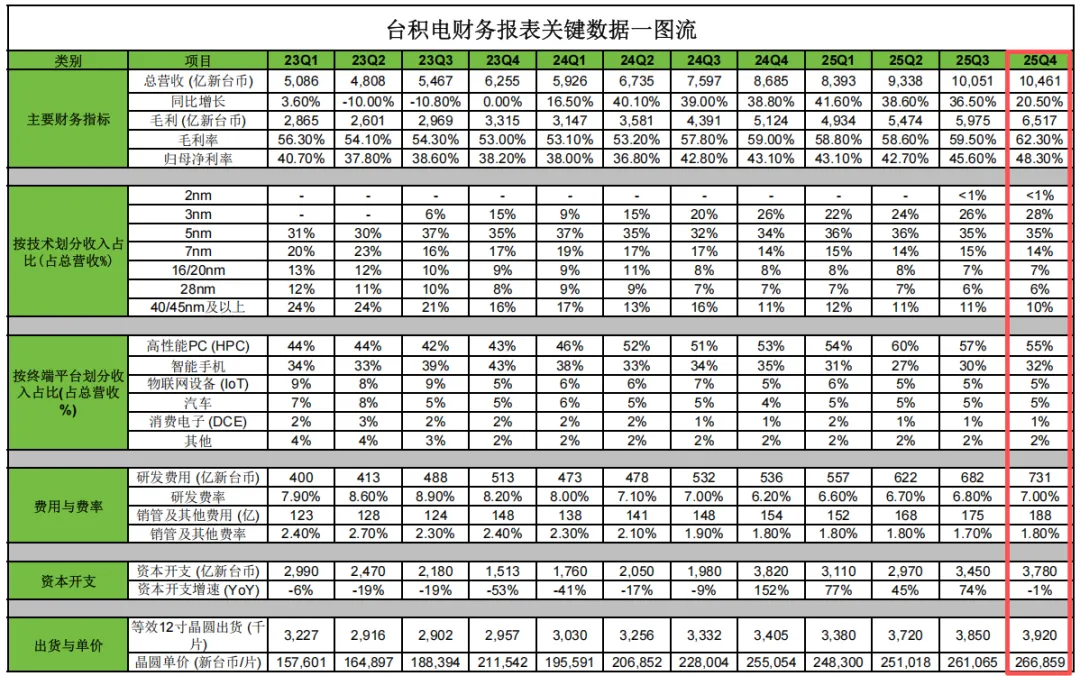

依据 2026 年 1 月 15 日发布的最新财报数据,台积电在 2025 年第四季度及全年均交出了令市场震惊的答卷。2025 年第四季度,台积电合并营收达到新台币 10,460.9 亿元(约 337.3 亿美元),同比增长 20.5%(以美元计价增长 25.5%);净利润达到新台币 5,057.4 亿元,同比增长 35.0%;毛利率达62.3%。这一业绩不仅显著超出了分析师的预期,更击穿了此前管理层指引的上限,显示出 AI 基础设施建设需求的“贪婪与无情” 。全年度来看,2025 年台积电总营收达到新台币 38,090.5 亿元,较 2024 年增长31.6%,美元营收增长 35.9% 。这一增长率远超全球半导体产业(不含存储)的平均增速。

AI 基础设施建设的“⽆情”需求

需求刚性:AI 模型参数量的指数级增⻓要求算⼒呈倍数扩张。Nvidia 的 Blackwell 架构芯⽚需求远超供给,⽽这些芯⽚ 100% 依赖台积电的 N4/N5/N3 ⼯艺 。

CoWoS 的倍增效应:AI 芯⽚不仅需要先进制程晶圆,还需要 CoWoS 先进封装来整合 HBM。台积电在 2025 年成功将 CoWoS 产能翻倍(达到⽉产 7.5 万⽚以上),解除了出货瓶颈。封装业务不仅带来了额外的营收,更通过提⾼成品芯⽚的附加值,锁定了客⼾粘性 。

技术垄断带来的极致定价权

在 2025 年,台积电在 5nm 和 3nm 节点上⼏乎没有竞争对⼿。

独家供应商地位:Samsung 在 3nm GAA 良率上挣扎,Intel Foundry 的 18A 尚未⼤规模量产,导致 Nvidia、AMD、Apple、Qualcomm 等⼤客⼾别⽆选择,只能将订单交给台积电。

价格传导机制:⾯对海外建⼚成本上升和通胀压⼒,台积电成功实施了涨价策略。分析指出,3nm 晶圆的单价⼤幅提升,且 CoWoS 服务价格也因供不应求⽽上涨。由于 AI 芯⽚本⾝⽑利极⾼(Nvidia ⽑利 >70%),客⼾对代⼯涨价并不敏感,这使得台积电的⽑利率能冲破62%

产能利⽤率与良率的“双击”

利⽤率满载:与 2023 年产能闲置导致⽑利承压不同,2025 年台积电的先进制程产能利⽤率⻓期维持在 100% 甚⾄超负荷运转。这极⼤地摊薄了巨额的折旧成本。

N3 良率爬坡:3nm ⼯艺在 2025 年进⼊成熟期。随着良率曲线的提升,报废率下降,直接转化为净利润的增加。这是 Q4 ⽑利率能够意外达到 62.3% 的重要技术原因 。

产品组合的⾼端化

营收增⻓不仅来⾃“量”的增加,更来⾃“质”的提升。随着 3nm 占⽐达到 24-28%,以及 HPC 占⽐接近 60%,台积电的产品组合向⾼单价、⾼⽑利⽅向剧烈倾斜。这种结构性改善使得营收增⻓速度快于晶圆出货量的增⻓速度 。

头部企业的财务图谱与运营韧性

中国晶圆代工双雄——中芯国际(SMIC)与华虹半导体呈现出“营收创新高、利润靠补贴”的典型特征 。

中芯国际:2025年Q3营收创历史新高(23.82亿美元),展现出强劲的增长韧性,且高度依赖本土市场(占比86.2%)。然而,由于缺乏EUV光刻机,推进先进制程需通过DUV多重曝光,导致折旧成本极高,政府补贴占其营业利润的近87% 。

华虹半导体:专注于特色工艺,营收稳步增长,但受成熟制程价格战影响,毛利率较巅峰期大幅下滑 。目前正处于“8英寸向12英寸”转型的战略阵痛期 。

制造工艺现状与核心“卡脖子”环节

中国在芯片制造领域呈现“单点突破、系统受阻”的局面 。

工艺突破:中芯国际已量产7nm(N+2)工艺,良率约60%-70% 。正在攻坚的5nm工艺面临物理极限,制造成本预计比台积电高出40%-50% 。

核心短板:

光刻机:国产化率仅约18%,EUV完全空白,浸没式DUV面临断供风险 。

EDA工具:在先进制程数字电路设计和GAA架构支持上仍存在缺失 。

半导体材料:高端光刻胶仍由日本企业垄断,国产一致性有待提升 。

局部突围:刻蚀设备(中微公司)和薄膜沉积设备(北方华创)国产化进展较快,已进入国际主流产线。

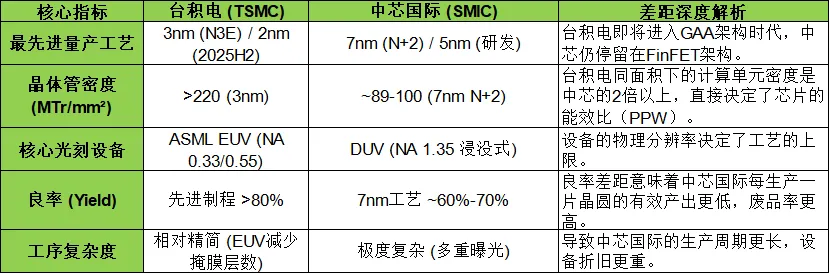

制造工艺差距量化:中芯国际 vs 台积电

中芯国际与台积电在技术代际上存在明显鸿沟 。

代际差距:台积电已进入3nm/2nm时代,而中芯国际稳定在7nm,量产时间落后约5年,技术代差约3个世代 。

关键指标对比 :

顶端AI芯片性能鸿沟:华为 vs 英伟达

在AI算力领域,国产芯片正艰难追赶 。

硬件性能:华为昇腾910B在算力上已基本持平英伟达A100,但显存带宽存在劣势 。下一代910C预计推理性能可达H100的60%-80% 。

致命短板:受限于国产HBM技术,存在明显的**“显存墙”**瓶颈;此外,集群互联技术(HCCS)在万卡规模下的效率不如英伟达的NVLink 。

软件生态:英伟达CUDA拥有深厚的护城河,华为CANN虽在快速迭代并开源,但在迁移成本和训练稳定性上仍面临挑战 。

缩短差距的战略路径:非对称突围

面对封锁,国内正在通过“组合拳”进行非对称竞争 。

先进封装(Chiplet):利用三维堆叠技术,以空间换时间,将成熟工艺的小芯片组合出高性能产品 。

软件定义性能:通过DeepSeek等厂商的底层算子优化,挖掘硬件潜能,弥补物理工艺不足 。

全产业链协同:组建“去美化”全栈国产产线,并利用国家大基金三期(3440亿元)重点投向光刻机、HBM等深水区环节 。

结合数据来看,台积电在“芯片制造”这个领域依然是“遥遥领先”、不可替代,至少在未来5-10年年内来看,国内的芯片制造企业依然难以对台积电构成较大的威胁。