半导体封装的作用、工艺和演变

祺芯半导体 2024-03-14 13:41

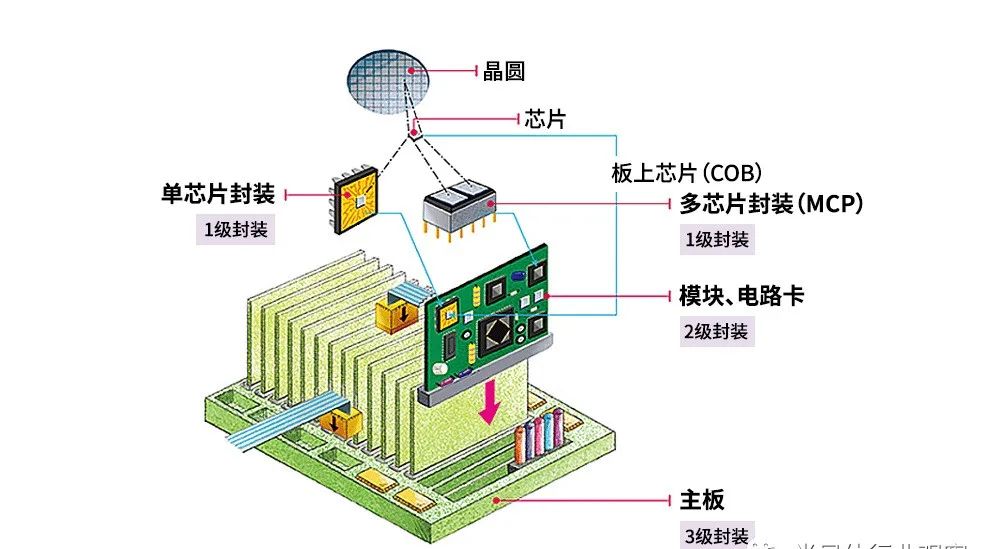

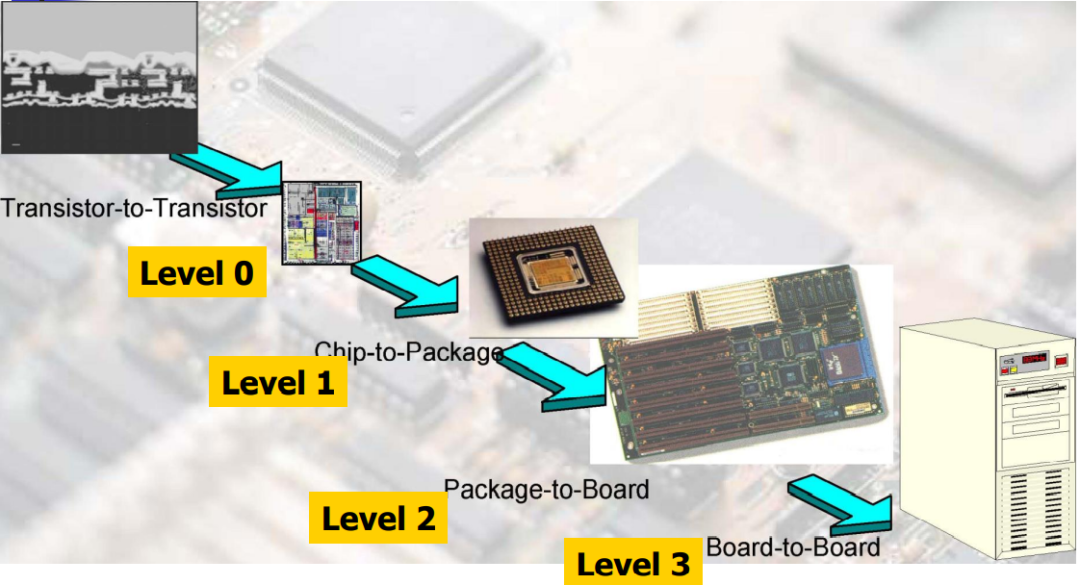

半导体封装工艺的四个等级

【1】有源元件:一种需要外部电源才能实现其特定功能的器件,就像半导体存储器或逻辑半导体。

【2】无源元件:一种不具备放大或转换电能等主动功能的器件。

【3】电容器(Capacitor):一种储存电荷并提供电容量的元件。

▲图1:半导体的封装等级

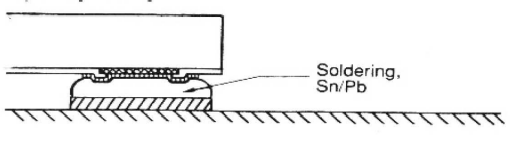

【4】锡(Solder):一种低熔点金属,支持电气和机械键合。

【5】引线(Lead):从电路或元件终端向外引出的导线,用于连接至电路板。

▲图2:半导体封装示例

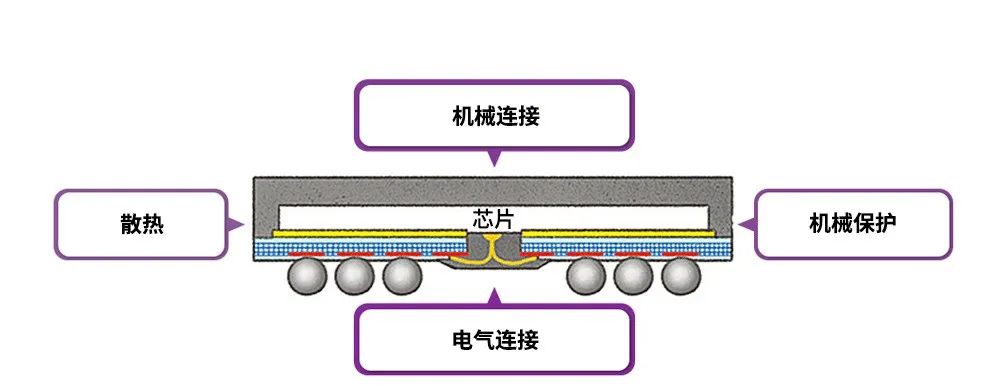

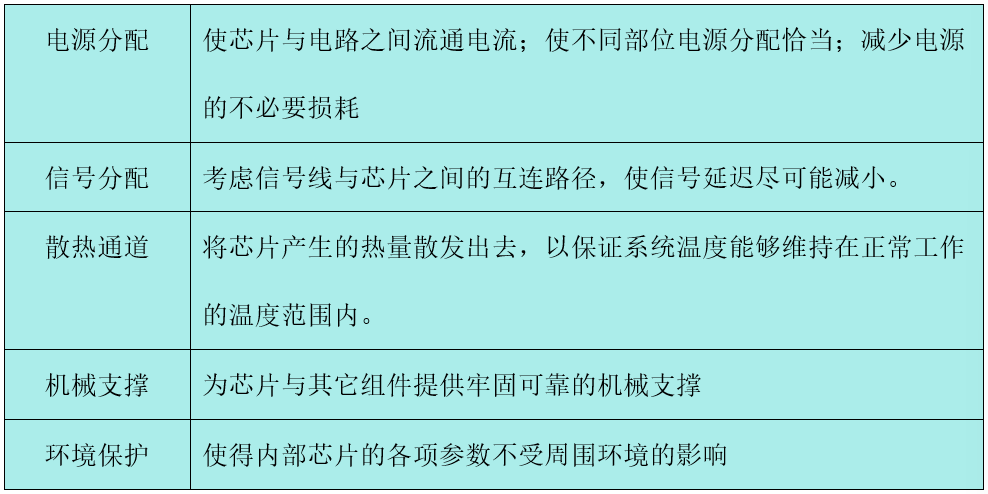

半导体封装的作用

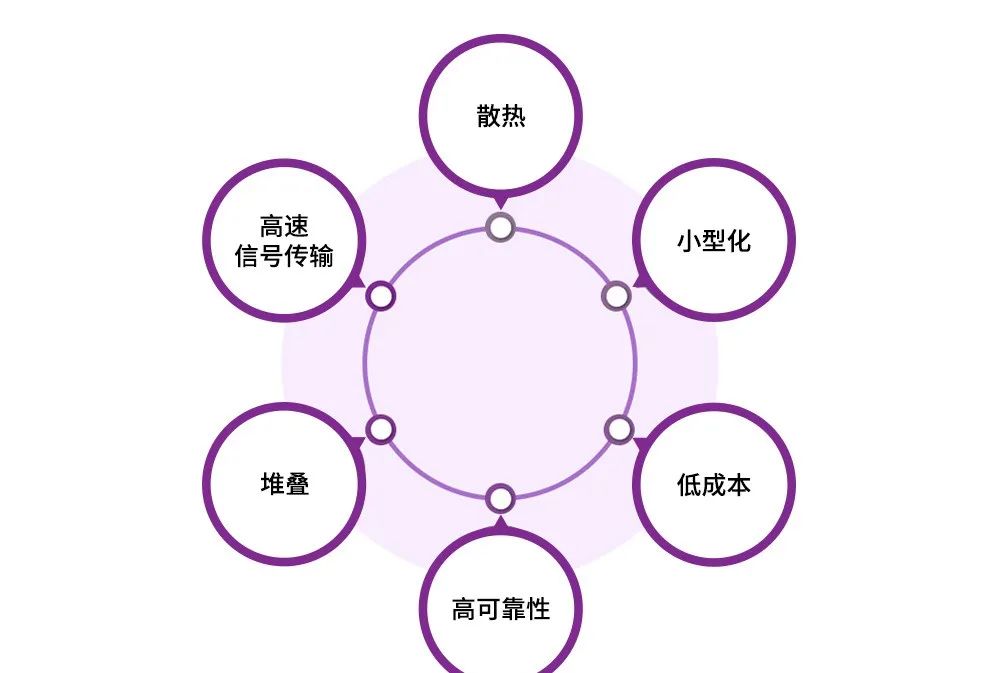

▲图3:半导体封装的作用

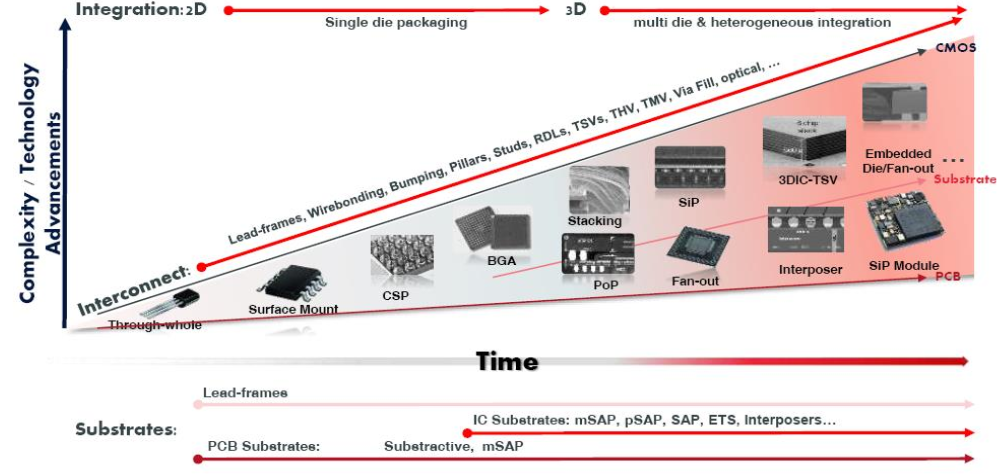

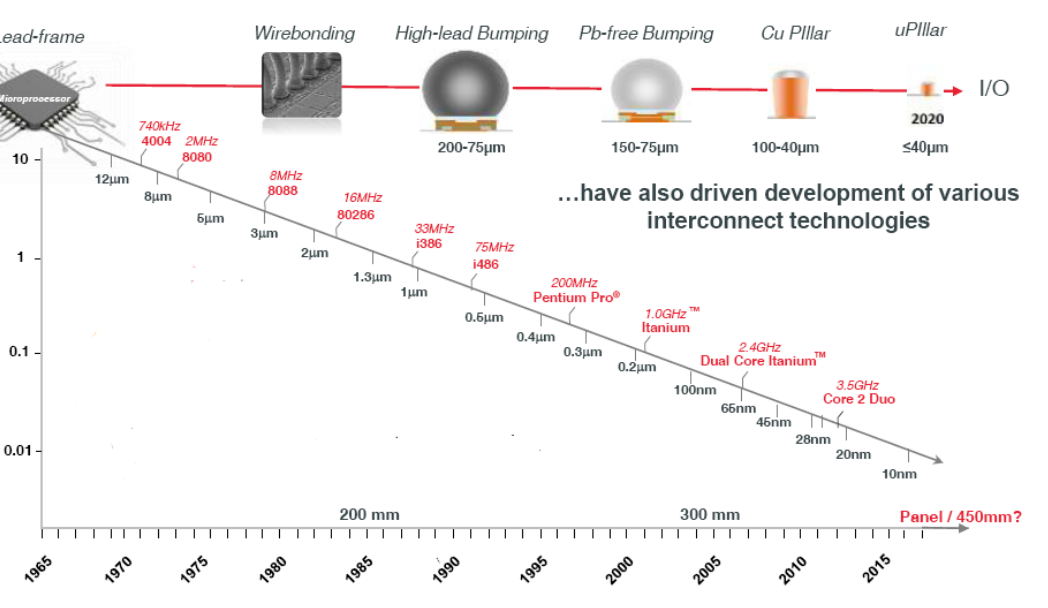

半导体封装的发展趋势

首先,由于散热已经成为封装工艺的一个重要因素,因此人们开发出了热传导【6】性能较好的材料和可有效散热的封装结构。

【6】热传导:指在不涉及物质转移的情况下,热量从温度较高的部位传递到相邻温度较低部位的过程。

可支持高速电信号传输的封装技术也成为了一种重要发展趋势,因为封装会限制半导体产品的速度。例如,将一个速度达每秒20千兆 (Gbps) 的半导体芯片或器件连接至仅支持每秒2千兆(Gbps) 的半导体封装装置时,系统感知到的半导体速度将为每秒2千兆 (Gbps)。由于连接至系统的电气通路是在封装中创建,因此无论芯片的速度有多快,半导体产品的速度都会极大地受到封装的影响。这意味着,在提高芯片速度的同时,还需要提升半导体封装技术,从而提高传输速度。这尤其适用于人工智能技术和5G无线通信技术。鉴于此,倒片封装【7】和硅通孔(TSV)【8】等封装技术应运而生,为高速电信号传输提供支持。

【7】倒片封装(Flip Chip):一种通过将凸点朝下安装于基板上,将芯片与基板连接的互连技术。

【8】硅通孔(TSV):一种可完全穿过硅裸片或晶圆实现硅片堆叠的垂直互连通道。

▲图4:半导体封装技术的发展趋势

【9】系统级封装(SiP):一种将多个器件整合在单个封装体内构成一个系统的封装技术。

【10】印刷电路板(PCB):由电路组成的半导体板,且元件焊接在电路板表面。这些电路板通常用于电子设备中。

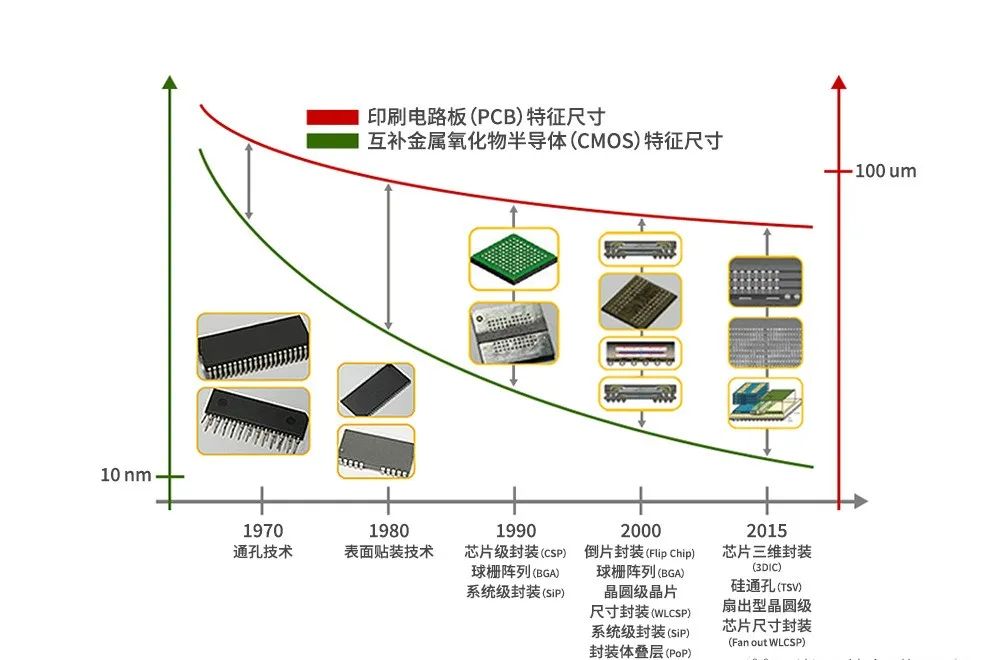

▲图5:随着时间的推移,晶圆和 印刷电路板特征尺寸的变化情况

通过测试确保半导体封装的有效性

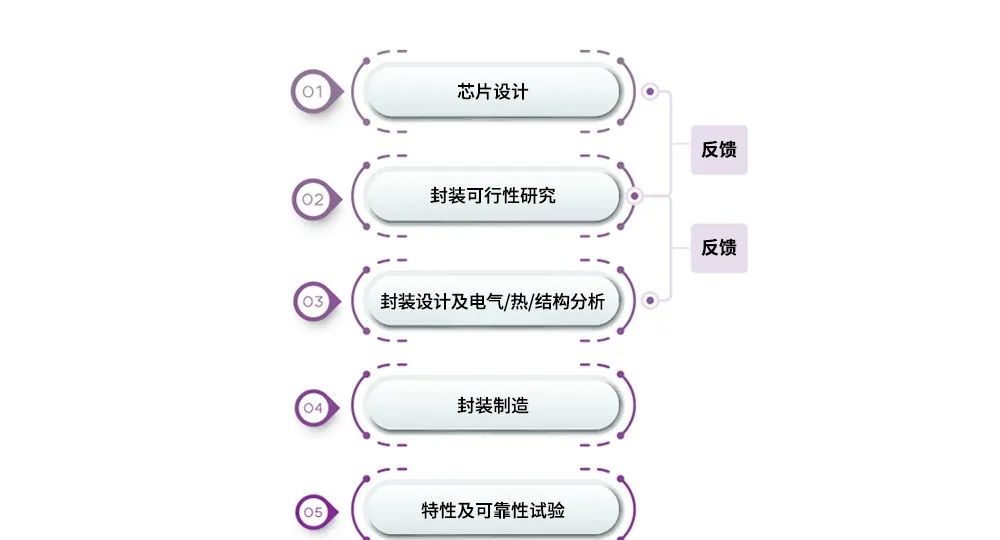

▲图6:半导体封装技术的开发流程

芯片封装工艺

祺芯半导体 2024-03-18 13:43

01引言

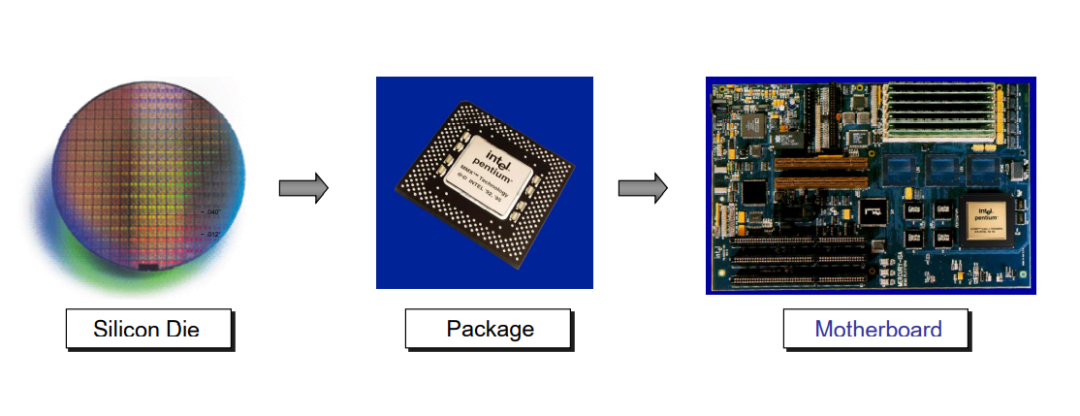

02何谓芯片封装

图 1 芯片封装的定位

图 2 芯片封装分级

03芯片封装的功能

表 1 芯片封装的五大功能

04芯片封装的几种技术

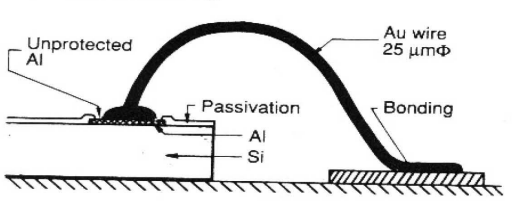

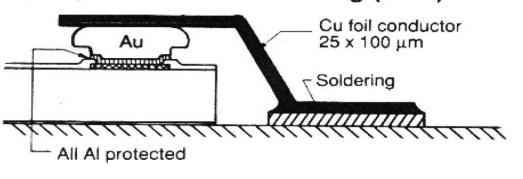

4.1 芯片互连技术

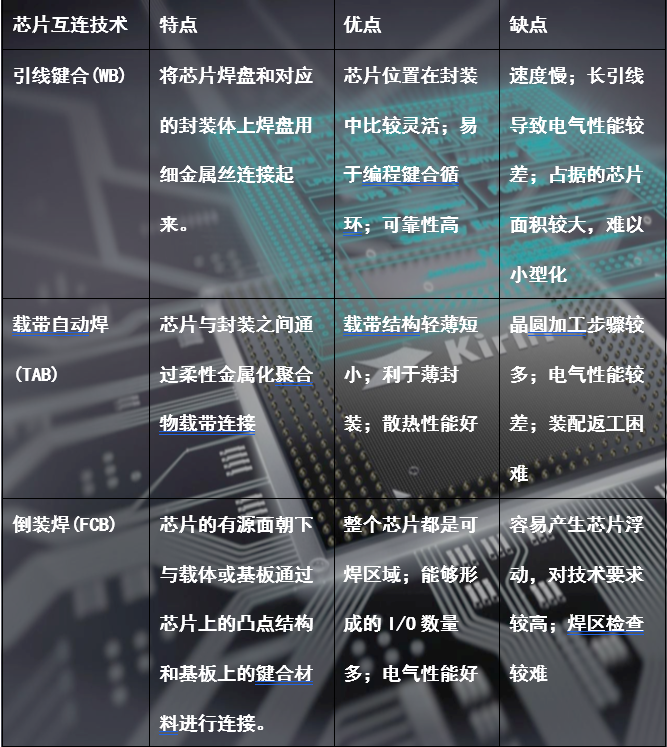

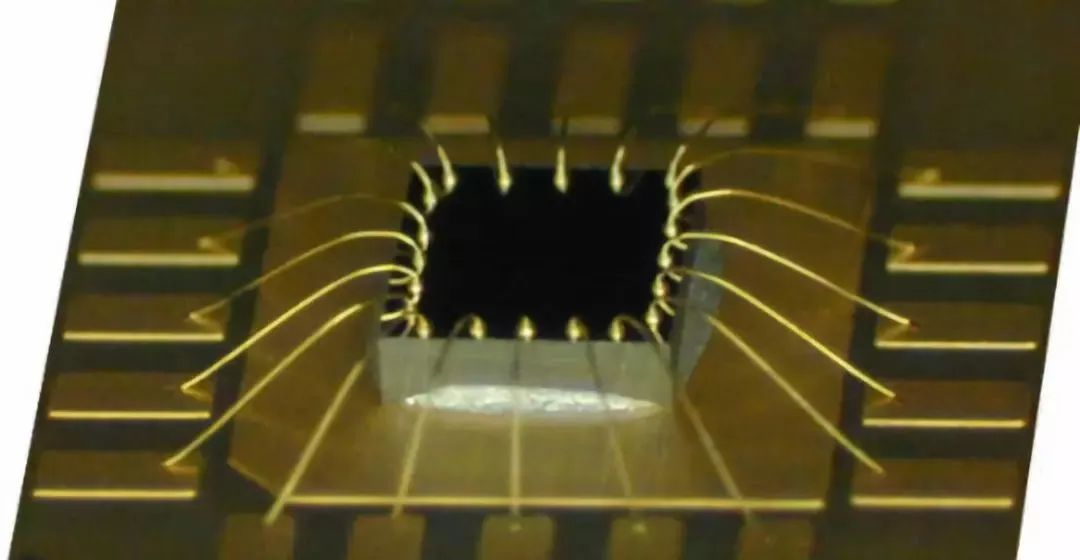

芯片互连技术来自与我们上文提到的零级封装,这是芯片与封装外壳以及外界环境建立联系的关键技术。芯片互连技术主要有三种:引线键合、载带自动焊以及倒装焊。

(a) 引线键合

(b) 载带自动焊

(c) 倒装焊

表 2 三种芯片互连技术对比

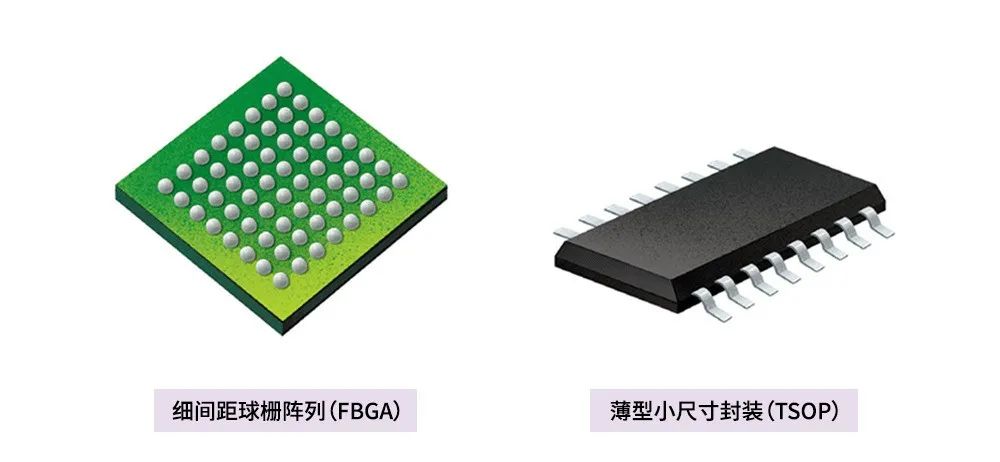

4.2 BGA封装技术

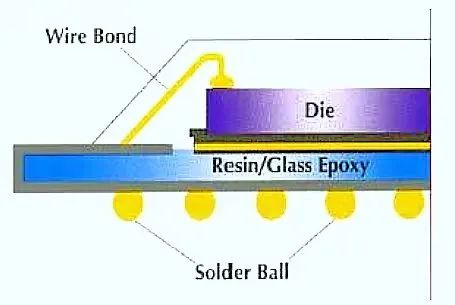

BGA(Ball Grid Array):球栅阵列。它是在基板的下边按面阵方式引出球形引脚,在基板上面贴装大规模集成电路芯片,是大规模集成电路芯片常用的一种表面贴装型封装形式。

优点:BGA封装的封装尺可以做的更小,同时也更节省PCB板的布线面积。

缺点:电路板的弯曲应力导致潜在的可靠性问题,BGA封装更容易受到压力

4.3 CSP封装技术

CSP(Chip Size Package),即芯片尺寸封装。是指封装尺寸不超过裸芯片1.2倍的一种先进的封装形式(美国JEDEC标准)。CSP技术是在对现有的芯片封装技术,其是对成熟的BGA封装技术做进一步技术提升的过程中,不断将各种封装尺寸进一步小型化而产生的一种封装技术。

优点:体积小;可容纳引脚数多;电性能良好;散热性能好

芯片制造和封测工艺简述

祺芯半导体 2024-02-04 13:19

一、硅晶圆制造与切割

晶圆是制作硅半导体IC所用之硅晶片,状似圆形,故称晶圆。材料是「硅」, IC(Integrated Circuit)厂用的硅晶片即为硅晶体,因为整片的硅晶片是单一完整的晶体,故又称为单晶体。但在整体固态晶体内,众多小晶体的方向不相,则为复晶体(或多晶体)。

晶圆是硅元素加以纯化,经过照相制版、研磨、抛光、切片等程序将多晶硅融解拉出单晶硅棒,然后切割成一片片晶圆。

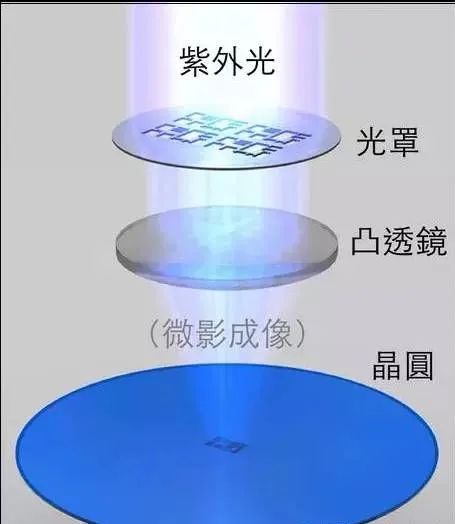

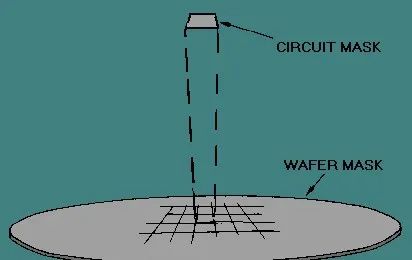

二、光学显影

光学显影是在感光胶上经过曝光和显影的程序,把光罩上的图形转换到感光胶下面的薄膜层或硅晶上。光学显影主要包含了感光胶涂布、烘烤、光罩对准、 曝光和显影等程序。

曝光方式有紫外线、X射线、电子束、极紫外光等。

三、蚀刻技术

蚀刻技术(Etching Technology)是将材料使用化学反应物理撞击作用而移除的技术。可以分为:

湿蚀刻(wet etching):湿蚀刻所使用的是化学溶液,在经过化学反应之后达到蚀刻的目的。

干蚀刻(dry etching):干蚀刻则是利用一种电浆蚀刻(plasma etching)。电浆蚀刻中蚀刻的作用,可能是电浆中离子撞击晶片表面所产生的物理作用,或者是电浆中活性自由基(Radical)与晶片表面原子间的化学反应,甚至也可能是以上两者的复合作用。

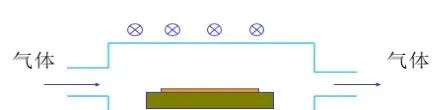

四、CVD化学气相沉积

这是利用热能、电浆放电或紫外光照射等化学反应的方式,在反应器内将反应物(通常为气体)生成固态的生成物,并在晶片表面沉积形成稳定固态薄膜(film)的一种沉积技术。CVD技术是半导体IC制程中运用极为广泛的薄膜形成方法,如介电材料(dielectrics)、导体或半导体等薄膜材料几乎都能用CVD技术完成。

常用的CVD技术有:

(1)常压化学气相沉积(APCVD);

(2)低压化学气相沉积(LPCVD);

(3)电浆辅助化学气相沉积(PECVD)

较为常见的CVD薄膜包括有:

■ 二气化硅(通常直接称为氧化层)

■ 氮化硅

■ 多晶硅

■ 耐火金属与这类金属之其硅化物

CVD的反应机制主要可分为五个步骤:

(1)在沉积室中导入气体,并混以稀释用的惰性气体构成「主气流(mainstream)」;

(2)主气流中反应气体原子或分子通过边界层到达基板表面;

(3)反应气体原子被「吸附(adsorbed)」在基板上;

(4)吸附原子(adatoms)在基板表面移动,并且产生化学反应;

(5)气态生成物被「吸解(desorbed)」,往外扩散通过边界层进入主气流中,并由沉积室中被去除。

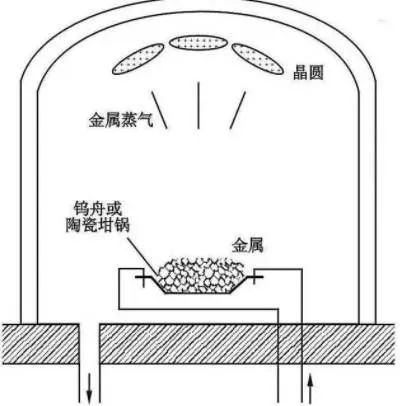

五、物理气相沉积(PVD)

这主要是一种物理制程而非化学制程。此技术一般使用氩等钝气,藉由在高真空中将氩离子加速以撞击溅镀靶材后,可将靶材原子一个个溅击出来,并使被溅击出来的材质(通常为铝、钛或其合金)如雪片般沉积在晶圆表面。

PVD以真空、测射、离子化或离子束等方法使纯金属挥发,与碳化氢、氮气等气体作用,加热至400~600℃(约1~3小时)后,蒸镀碳化物、氮化物、氧化物及硼化物等1~10μm厚之微细粒状薄膜。

PVD可分为三种技术:

(1)蒸镀(Evaporation);(2)分子束磊晶成长(Molecular Beam Epitaxy;MBE);(3)溅镀(Sputter)

解离金属电浆是最近发展出来的物理气相沉积技术,它是在目标区与晶圆之间,利用电浆,针对从目标区溅击出来的金属原子,在其到达晶圆之前,加以离子化。离子化这些金属原子的目的是,让这些原子带有电价,进而使其行进方向受到控制,让这些原子得以垂直的方向往晶圆行进,就像电浆蚀刻及化学气相沉积制程。这样做可以让这些金属原子针对极窄、极深的结构进行沟填,以形成极均匀的表层,尤其是在最底层的部份。

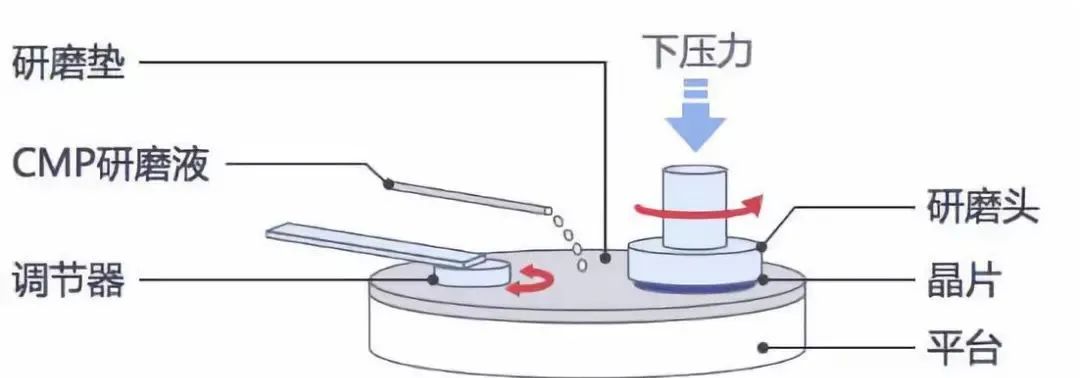

六、化学机械研磨技术

化学机械研磨技术(化学机器磨光, CMP)兼具有研磨性物质的机械式研磨与酸碱溶液的化学式研磨两种作用,可以使晶圆表面达到全面性的平坦化,以利后续薄膜沉积之进行。

在CMP制程的硬设备中,研磨头被用来将晶圆压在研磨垫上并带动晶圆旋转,至于研磨垫则以相反的方向旋转。在进行研磨时,由研磨颗粒所构成的研浆会被置于晶圆与研磨垫间。影响CMP制程的变量包括有:研磨头所施的压力与晶圆的平坦度、晶圆与研磨垫的旋转速度、研浆与研磨颗粒的化学成份、温度、以及研磨垫的材质与磨损性等等。

七、光罩检测

光罩是高精密度的石英平板,是用来制作晶圆上电子电路图像,以利集成电路的制作。光罩必须是完美无缺,才能呈现完整的电路图像,否则不完整的图像会被复制到晶圆上。光罩检测机台则是结合影像扫描技术与先进的影像处理技术,捕捉图像上的缺失。

当晶圆从一个制程往下个制程进行时,图案晶圆检测系统可用来检测出晶圆上是否有瑕疵包括有微尘粒子、断线、短路、以及其它各式各样的问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。

一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。

八、清洗

清洗的目的是去除金属杂质、有机物污染、微尘与自然氧化物;降低表面粗糙度;因此几乎所有制程之前或后都需要清洗。

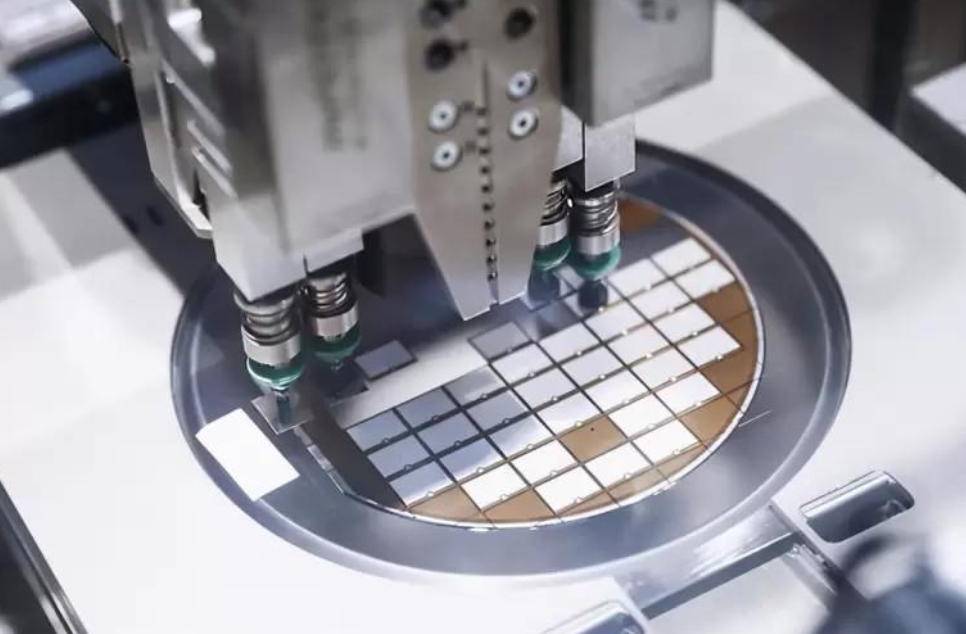

九、晶片切割(Die Saw)

晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。首先必须进行晶圆黏片,在晶圆上贴一层胶带,然后送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撑避免了胶带的皱摺与晶粒之相互碰撞。

十:焊线(Wire Bond)

将集成电路内部的线路引出,并向外拉出引线,称之为打线,作为与外界电路板连接之用。

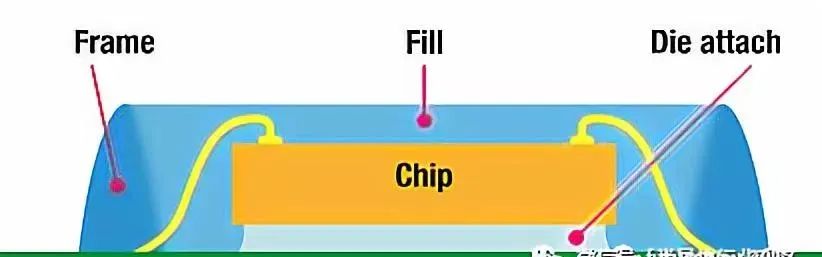

十一、封胶(Mold)

封胶之主要目的为防止湿气由外部侵入、以机械方式支 持导线、内部产生热量之去除及便于手持。其过程为将导线架置于框架上并预热,再将框架置于压模机上的构装模上,再以树脂充填并待硬化。

十二、剪切/成形(Trim /Form)

剪切之目的为将导线架上构装完成之晶粒独立分开,并把不需要的连接用材料及部份凸出之树脂切除(dejunk)。成形之目的则是将外引脚压成各种预先设计好之形状,以便于装置于电路版上使用。

十三:芯片测试和检验过程

这些测试和检验就是保证封装好芯片的质量,保证其良率的。

芯片设计-晶圆代工-封测三部曲产业链

祺芯半导体 2024-02-07 09:30

一、芯片设计

集成电路是电子信息产业的基石,而IC设计作为集成电路产业链上游,是最具发展活力和创新的重要环节,具有高投入、高风险、高产出的特点。

资料来源:SEMI

资料来源:SEMI

1.芯片设计 - 芯片制造主产业链关键环节

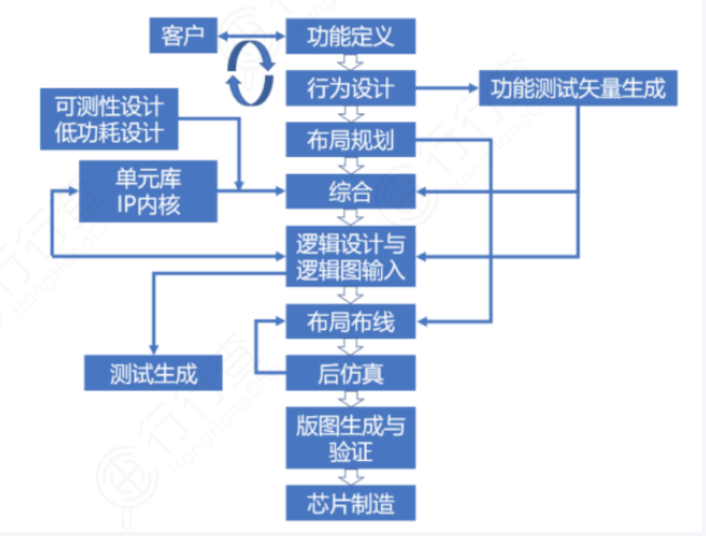

2.芯片设计流程

芯片设计流程主要可分为前端设计(Front end)与后端设计(Backend),其中前端设计(也称为逻辑设计)主要涉及芯片的功能设计,后端设计(也称为物理设计)主要涉及工艺有关的设计,使其成为具备制造意义的芯片。

芯片设计和生产流程图:

芯片设计运作模式上世纪80年代,电子行业出现了几种新的分工模式,包括IDM模式、Fabless模式和Fundary模式。

3.芯片设计竞争格局

IC设计行业中少数巨头企业占据了主导地位,其中美国IC设计行业处于领先地位。国内半导体产业链上游芯片设计环节公司主要涉及的领域包括存储芯片、射频芯片、图像传感器芯片、生物识别芯片、模拟器件芯片、WiFi芯片等,以及功率芯片、电源控制芯片、功能控制芯片等多个领域。国内芯片设计总体来说体量尚小,芯片设计企业与全球主要对标企业的营收差距较大,大部分企业不到对标企业营收规模5%。相比之下,国外细分领域的芯片设计龙头公司收入基本都在上百亿美金的水平。

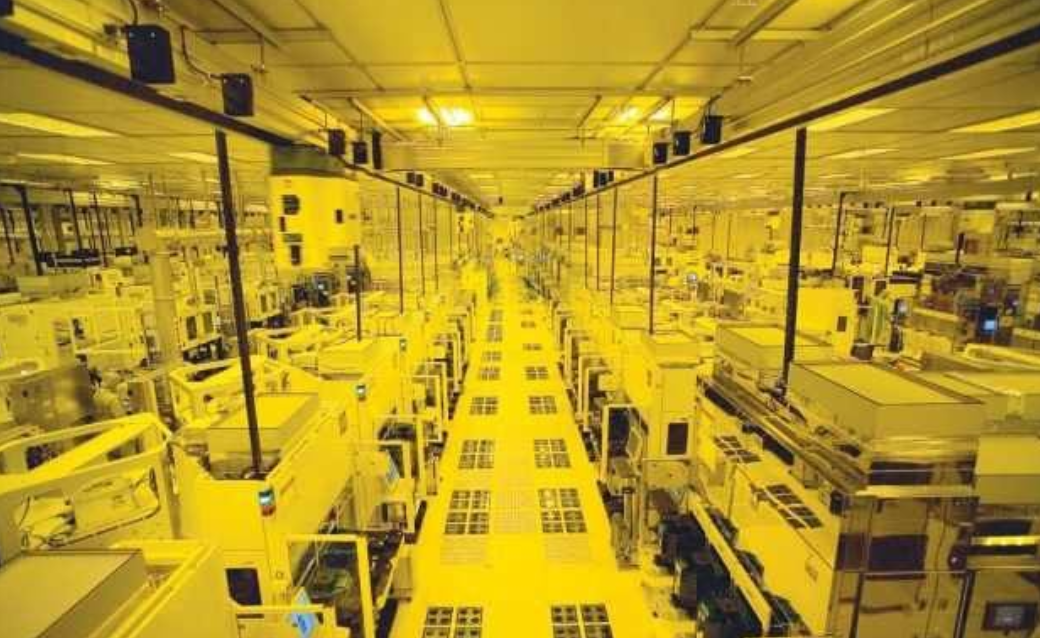

二、半导体晶圆代工

自2020年下半年以来,晶圆代工产能持续紧张,在驱动IC和功率器件等需求刺激下,主要晶圆代工产能利用率均超过95%,维持较高位置。

晶圆制造是半导体产业最关键、市场份额最大的核心环节。主要以晶圆为原材料,将光掩模上的电路图形信息大批量复制到晶圆上,并在晶圆上大批量形成特定集成电路结构的过程,其技术含量高、工艺复杂,在芯片生产过程中处于至关重要的地位。

三、半导体封测

封测行业位于集成电路产业链末端,是劳动密集型行业。作为我国半导体领域优势最为突出的子行业,在当前国产半导体产业链中,国产化程度最高、行业发展最为成熟。

随着上游的芯片设计公司选择将订单回流到国内,大批新建晶圆厂产能的释放以及国内主流代工厂产能利用率的提升,晶圆厂的产能扩张也势必蔓延至中下游封装厂商,将带来更多的半导体封测新增需求。

▌封装测试产业链

封装测试位于半导体产业链的中下游,包括封装和测试两个环节。

根据Gartner测算,封装和测试在整个封测流程中的市场份额占比约为80%~85%和15%~20%。

封装是对制造完成的晶圆进行划片、贴片、键合、电镀等一系列工艺,以保护晶圆上的芯片免受物理、化学等环境因素造成的损伤,增强芯片的散热性能,以及将芯片的I/O端口引出的半导体产业环节。

无锡祺芯半导体科技有限公司是专业从事芯片行业智能化生产设备的研发、生产和销售的高科技企业。成立于2020年,座落在无锡惠山经济技术开发区。公司获得无锡惠山区先锋人才,无锡市太湖人才等多项荣誉,是无锡市半导体协会理事单位。公司研发团队核心人员,均拥有20年以上半导体设备从业经验,对封装工艺及相关装备产业化拥有丰富研发经验,拥有多项国家级技术发明、实用新型专利和软件著作权。并与清华大学、中国科学院等国内知名院校长期进行产学研合作。

公司自主研发的MGP智能芯片封装系统、AM全自动芯片封装系统、TF单元组合式芯片自动切筋成型系统等多款芯片智能化生产设备,均已获得市场认可和客户的一致好评。

无锡祺芯半导体科技有限公司,秉承创新、高效、品质、诚信的价值观,立足无锡,以做中国自主品牌的芯片智能设备为使命,助力芯片产业,打造智慧工厂。立志成为芯片封测设备行业的领航者!