本文结合瑞芯微官方设计文档,详细总结时钟电路的原理图设计要点与 PCB 布局布线规范。

福利领取:文章结尾可免费获取《RK3588PCB设计指导白皮书》和RK3576/RK3568/RK3588学习视频相关资料

1、时钟电路原理图

1.1、核心系统时钟设计(24MHz时钟)

1.1.1、电路构成

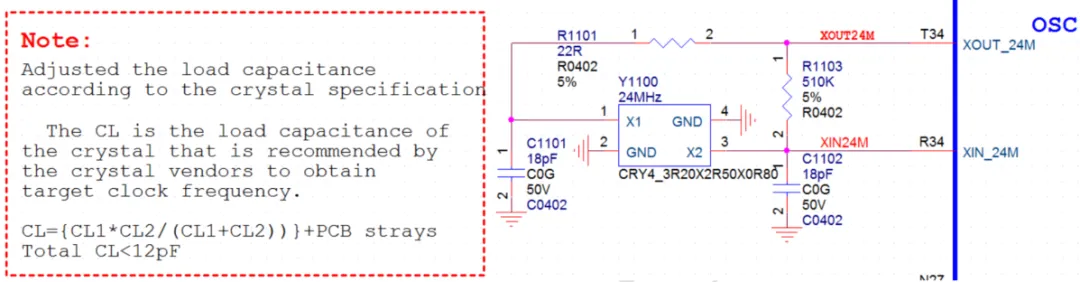

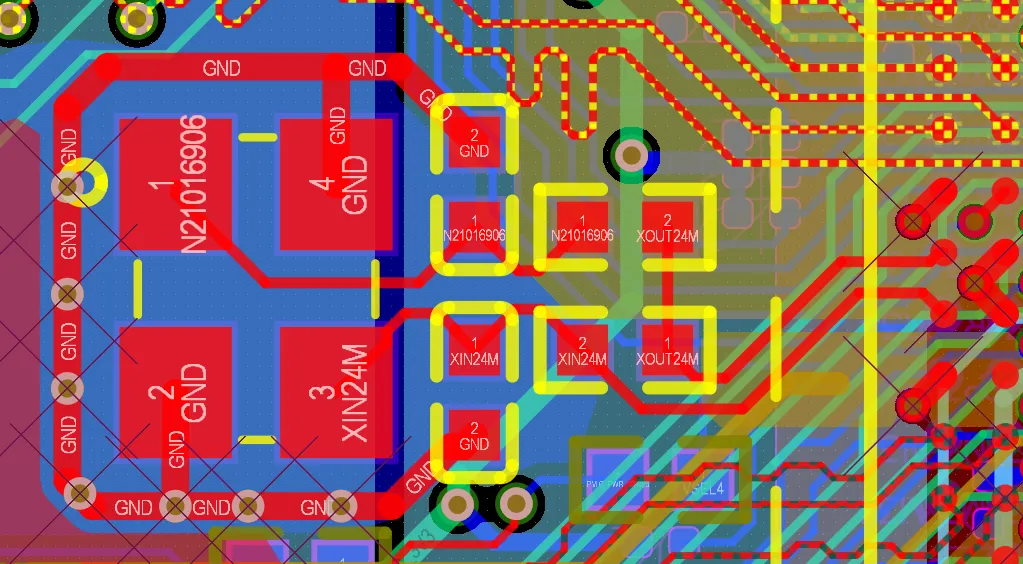

RK3588 内部振荡器与外置 24MHz 晶振配合,形成系统主时钟,是芯片核心工作时序的基础。

1.1.2、关键器件要求

1、晶振选择:负载电容 CL 值≤12pF,常温下频率容限≤20ppm;推荐采用贴片 4Pin 晶振,其中 2 个 GND 管脚需与 PCB 地充分连接,增强抗 ESD 能力。 2、匹配电阻:XOUT24M 网络必须串接 22Ω 限流电阻,防止过驱;XOUT24M 与 XIN24M 之间的 510KΩ 电阻不可随意修改。 3、负载电容:需根据晶体规格书选择(文档示例为 18pF),材质优先采用 COG 或 NPO,满足 CL=(CL1×CL2/(CL1+CL2))+PCB 寄生电容的计算关系。

1.2、待机时钟设计(32.768KHz 时钟)

1.2.1、功能作用

芯片待机时可切换为 32.768KHz 时钟,关闭 OSC 振荡电路,降低待机功耗,仅支持 PMUIO1 和 PMUIO2 电源域的 IO 中断唤醒。

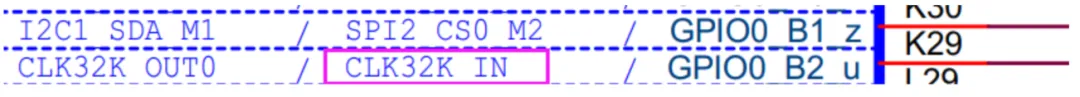

1.2.2、时钟来源

可从外置 RTC 时钟源获取,输入管脚需配置为 CLK32K_IN 功能,输入幅度需匹配 PMUIO1 域供电电压。

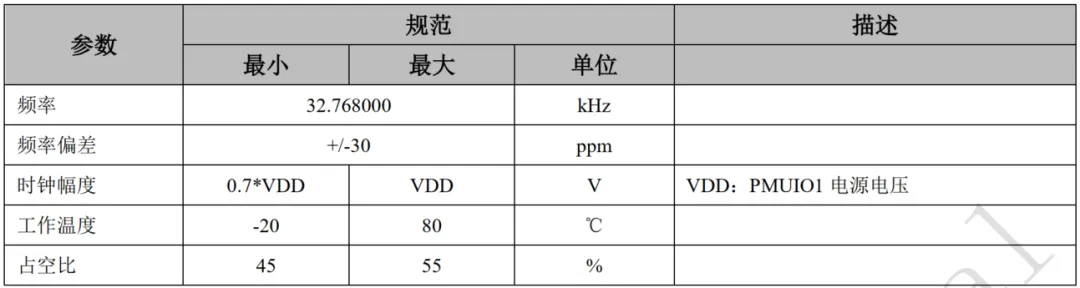

1.2.3、关键参数

频率固定为 32.768kHz

频率偏差 ±30ppm

工作温度 - 20 ~ 80℃

占空比 45%~55%。

1.3、外设时钟输出功能

RK3588 可向外设提供多路时钟,需注意 IO 域电平与外设匹配:

- 1、REFCLK_OUT: 预留时钟输出引脚, 根据实际需求选用;

- 2、CLK32K_OUT0: 32.768KHz 时钟输出,可提供给 WIFI, BT, PCIe 等设备当休眠或工作时钟;

- 3、CLK32K_OUT1: 32.768KHz 时钟输出,可提供给 WIFI, BT, PCIe 等设备当休眠或工作时钟;

- 4、ETH0_REFCLKO_25M: 25MHz 时钟输出,可提供给 Ethernet PHY 等设备当工作时钟;

- 5、ETH1_REFCLKO_25M: 25MHz 时钟输出,可提供给 Ethernet PHY 等设备当工作时钟;

- 6、MIPI_CAMERA0_CLK------MIPI_CAMERA4_CLK:默认 24MHz 时钟输出,可提供给 Camera 等设备当工作时钟;也可根据 PLL 分频得到其它频点, 并且每路时钟支持各自输出不同的频率;

- CIF_CLKOUT: 默认 24Mhz 时钟输出,可根据 PLL 分频得到其它频点,可提供给 Camera 等设备当做工作时钟。

2、时钟电路PCB

2.1、布局核心要求

1、优先布局原则:晶体电路需优先规划,整体布局紧凑,晶体与 RK3588 芯片同层放置且尽量靠近,避免打过孔,缩短走线长度。 2、隔离与远离:晶体及时钟器件需远离板边缘、接口电路(距离≥10mm)、大功率器件、散热器及 RF 干扰源(如 WIFI/BT 模块)。 3、敏感模块隔离:若存在多个敏感模块(如射频、音频、存储器),可添加屏蔽罩,且屏蔽罩需可靠接地。

2.2、布线关键规范

1、包地处理:晶体走线及所有时钟信号需全程包地,包地线每隔 200~300mil 至少添加一个 GND 过孔,确保邻层地参考面完整;也可在晶体当前层围绕其绘制 GND 地环,地环上放置 GND 过孔连接相邻 GND 平面。 2、走线禁忌:Xin 与 Xout 走线及晶体下方投影区域禁止任何其他走线,避免噪声耦合;时钟走线不得跨分割,相邻层需为完整参考平面,防止阻抗突变。 3、换层处理:若晶体与芯片必须异层放置,需缩短走线长度并全程包地;时钟信号换层时,需在过孔旁添加回流地过孔,保证回流路径连续。

结束福利

1、微信扫码关注 擎天柱工坊

2、发送消息 RK3588白皮书 或者 RK3576硬件设计 或者 RK3568硬件设计 或者 RK3588硬件设计