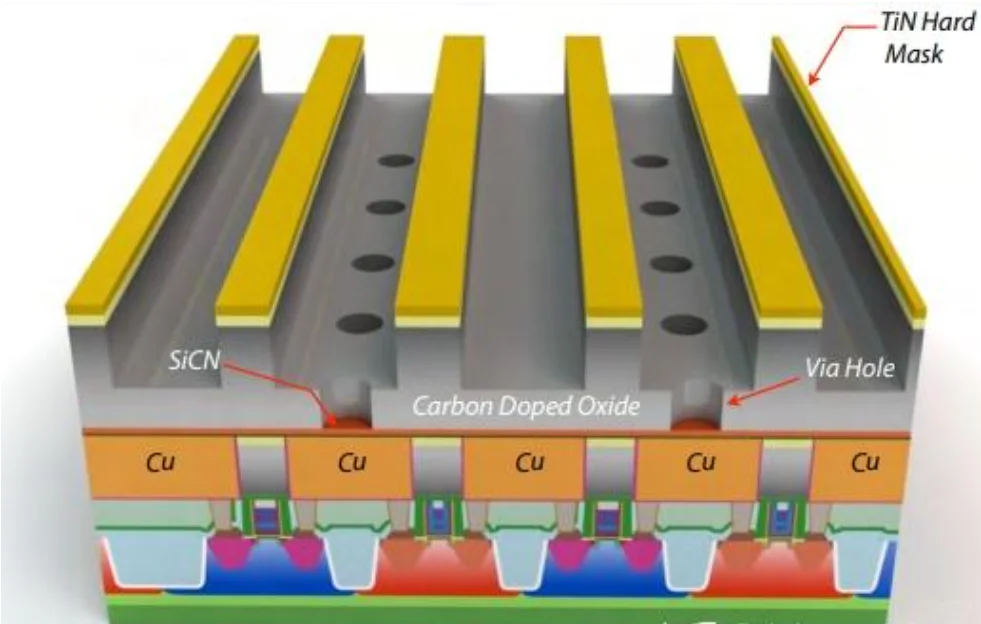

在半导体制造领域,大马士革镶嵌工艺是一种极为重要的铜图形化工艺,特别是在集成电路制造中的铜布线环节。随着工艺节点不断演进,该工艺的应用愈发广泛。在大马士革镶嵌工艺体系下,Via first(通孔优先)和 Trench first(沟槽优先)两种工艺方法因各有特点,成为了关注的焦点。

工艺流程差异

Via first 工艺

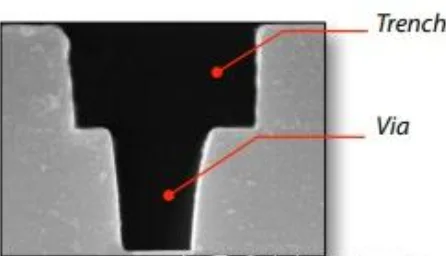

Via first 工艺,顾名思义,是先进行通孔的蚀刻。首先,在已沉积好的介电层上,利用光刻技术确定通孔的位置,随后通过蚀刻工艺形成通孔。完成通孔制作后,再进行导线用沟槽的蚀刻。这种工艺顺序使得通孔的光刻制程相对容易,因为是在较为平坦的介电层表面进行,光刻的工艺视窗(process window)较大,对光刻设备和工艺控制的精度要求相对较低。不过,由于光刻过程中使用的光阻和 ARC 抗反射层,在通孔蚀刻完成后,孔洞内可能会残留有机物质,后续需要额外的清洗工艺步骤来确保通孔内部的洁净度,以免影响后续金属填充的质量和电气性能。

Trench first 工艺则是反其道而行之,最先在已沉积的介电层上蚀刻出导线用的沟槽。完成沟槽蚀刻后,进行孔洞的光刻,最后蚀刻出孔洞。由于先蚀刻沟槽,后续光刻孔洞时光阻需要覆盖在已形成的沟槽之上,导致孔洞处的光阻较厚,这大大增加了曝光和显影的难度,对光刻设备的光源强度、分辨率以及光刻胶的性能都提出了很高要求。为防止在蚀刻孔洞时过度蚀刻对下方介电层造成损坏,通常会在介电层下方添加蚀刻终止层,这无疑增加了工艺流程的复杂性和成本。

Trench first的缺点在于Via的光刻时,由于PR会填充在trench里面,导致PR较厚,造成曝光(exposure)和显影(development)较困难。

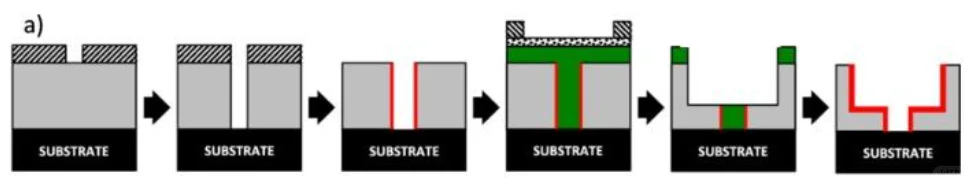

trench and via all in one顾名思义就是trench和via一起蚀刻,此方法涉及一层硬掩膜(hard mask)的蚀刻,首先还是电介质的沉积,然后再沉积一层HM,接着铺PR,曝光、显影定义出trench的图形,然后是对HM的蚀刻,接着再铺PR,曝光、显影定义出Via的图案,这里HM相当于trench的PR,最后进行trench和via同时蚀刻,一步制程同时完成trench和via的图案。这一般适用在40nm以下先进工艺。

后续内容,关注W X 国芯制造

工艺流程差异

Via first 工艺

Via first 工艺,顾名思义,是先进行通孔的蚀刻。首先,在已沉积好的介电层上,利用光刻技术确定通孔的位置,随后通过蚀刻工艺形成通孔。完成通孔制作后,再进行导线用沟槽的蚀刻。这种工艺顺序使得通孔的光刻制程相对容易,因为是在较为平坦的介电层表面进行,光刻的工艺视窗(process window)较大,对光刻设备和工艺控制的精度要求相对较低。不过,由于光刻过程中使用的光阻和 ARC 抗反射层,在通孔蚀刻完成后,孔洞内可能会残留有机物质,后续需要额外的清洗工艺步骤来确保通孔内部的洁净度,以免影响后续金属填充的质量和电气性能。

Trench first 工艺则是反其道而行之,最先在已沉积的介电层上蚀刻出导线用的沟槽。完成沟槽蚀刻后,进行孔洞的光刻,最后蚀刻出孔洞。由于先蚀刻沟槽,后续光刻孔洞时光阻需要覆盖在已形成的沟槽之上,导致孔洞处的光阻较厚,这大大增加了曝光和显影的难度,对光刻设备的光源强度、分辨率以及光刻胶的性能都提出了很高要求。为防止在蚀刻孔洞时过度蚀刻对下方介电层造成损坏,通常会在介电层下方添加蚀刻终止层,这无疑增加了工艺流程的复杂性和成本。

Trench first的缺点在于Via的光刻时,由于PR会填充在trench里面,导致PR较厚,造成曝光(exposure)和显影(development)较困难。

trench and via all in one顾名思义就是trench和via一起蚀刻,此方法涉及一层硬掩膜(hard mask)的蚀刻,首先还是电介质的沉积,然后再沉积一层HM,接着铺PR,曝光、显影定义出trench的图形,然后是对HM的蚀刻,接着再铺PR,曝光、显影定义出Via的图案,这里HM相当于trench的PR,最后进行trench和via同时蚀刻,一步制程同时完成trench和via的图案。这一般适用在40nm以下先进工艺。

后续内容,关注W X 国芯制造