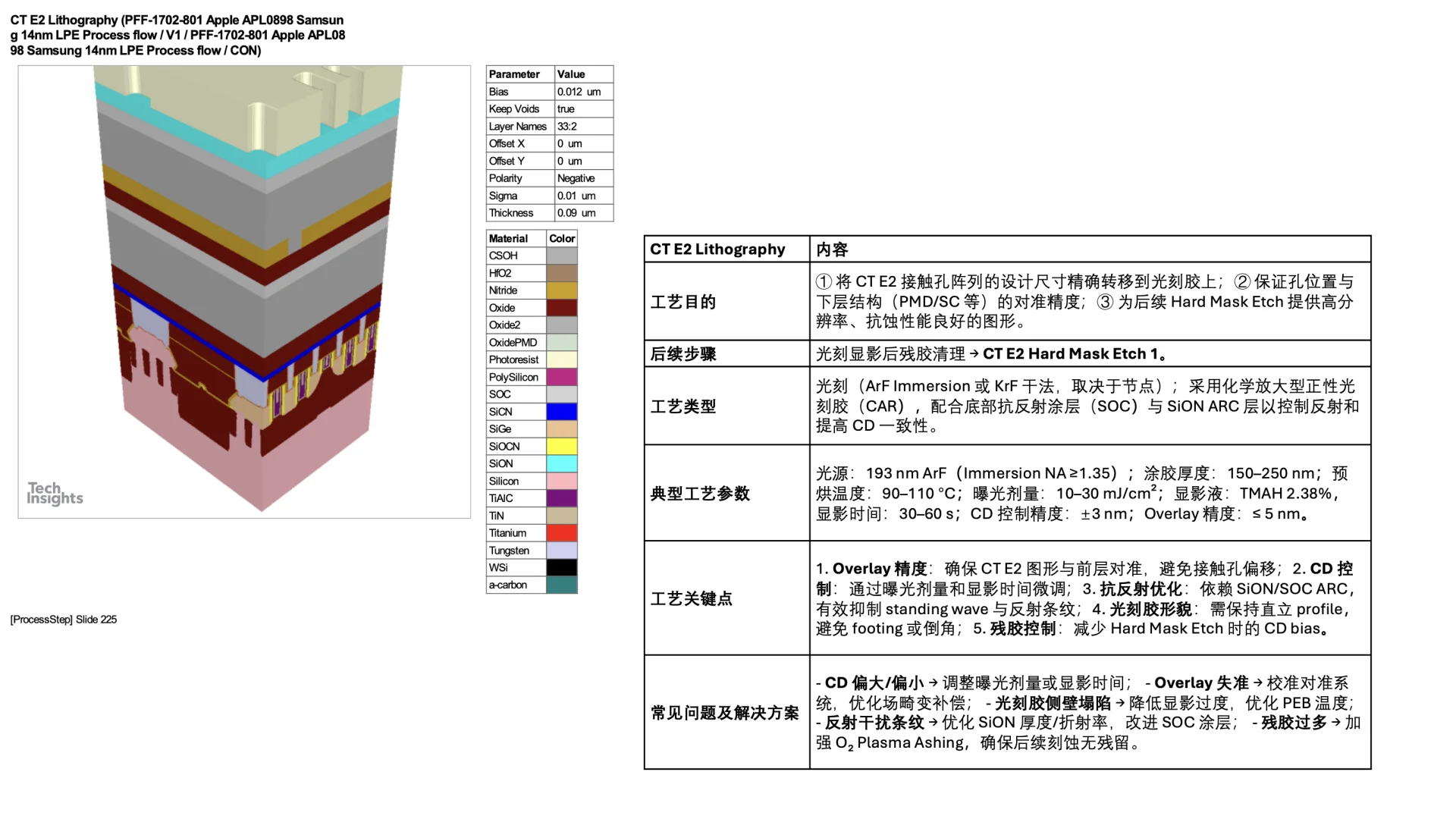

在 14nm FinFET 工艺中,CT E2(Contact Etch 2)主要目的是实现更精细、垂直性更好的接触窗口刻蚀,为后续金属接触(如 W 填充)提供高保真度的图形。该流程通过多层材料涂布、刻蚀与去除的组合,逐步确保接触孔在高深宽比结构下具备良好的形貌与可靠性。

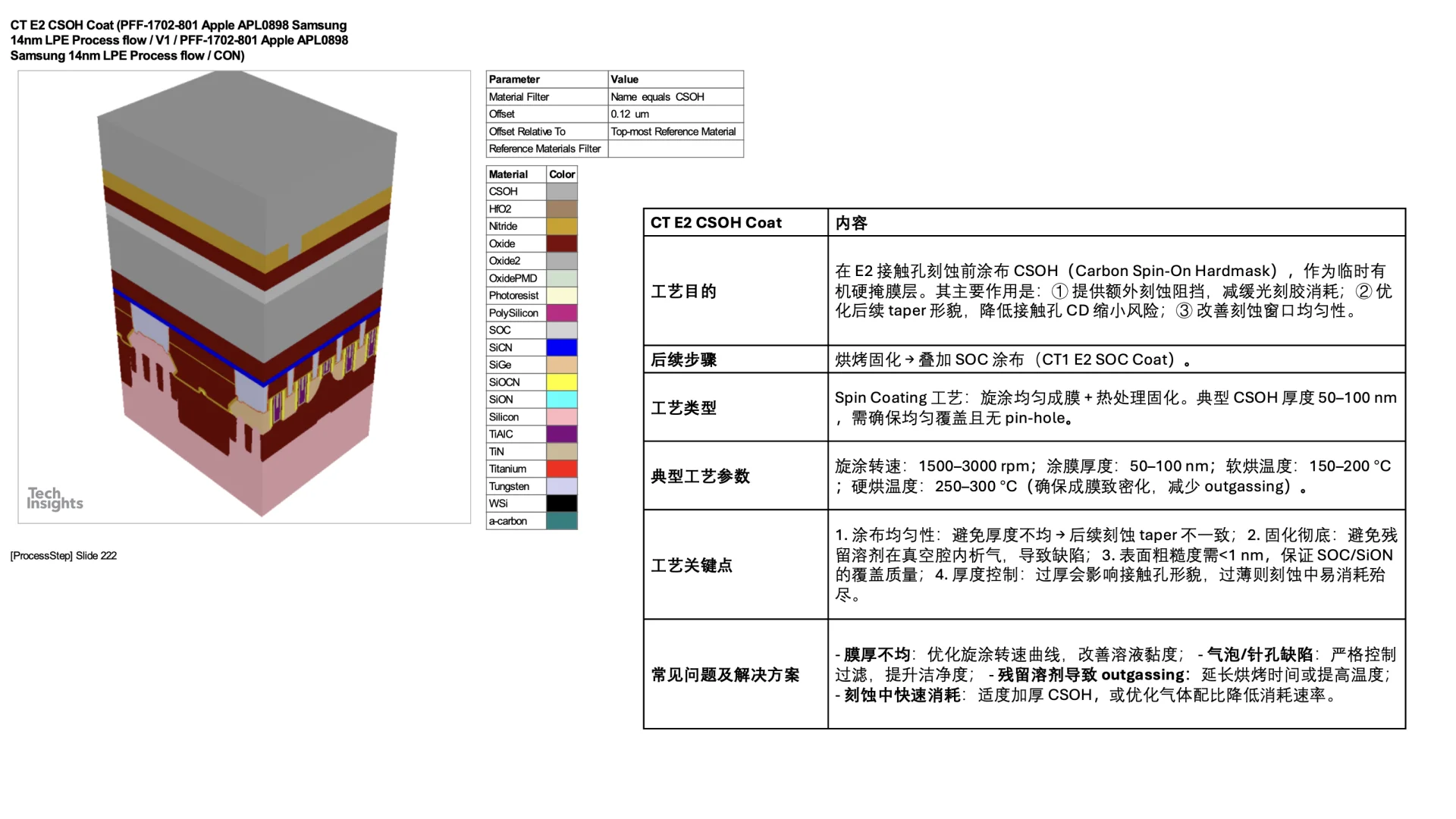

材料堆叠

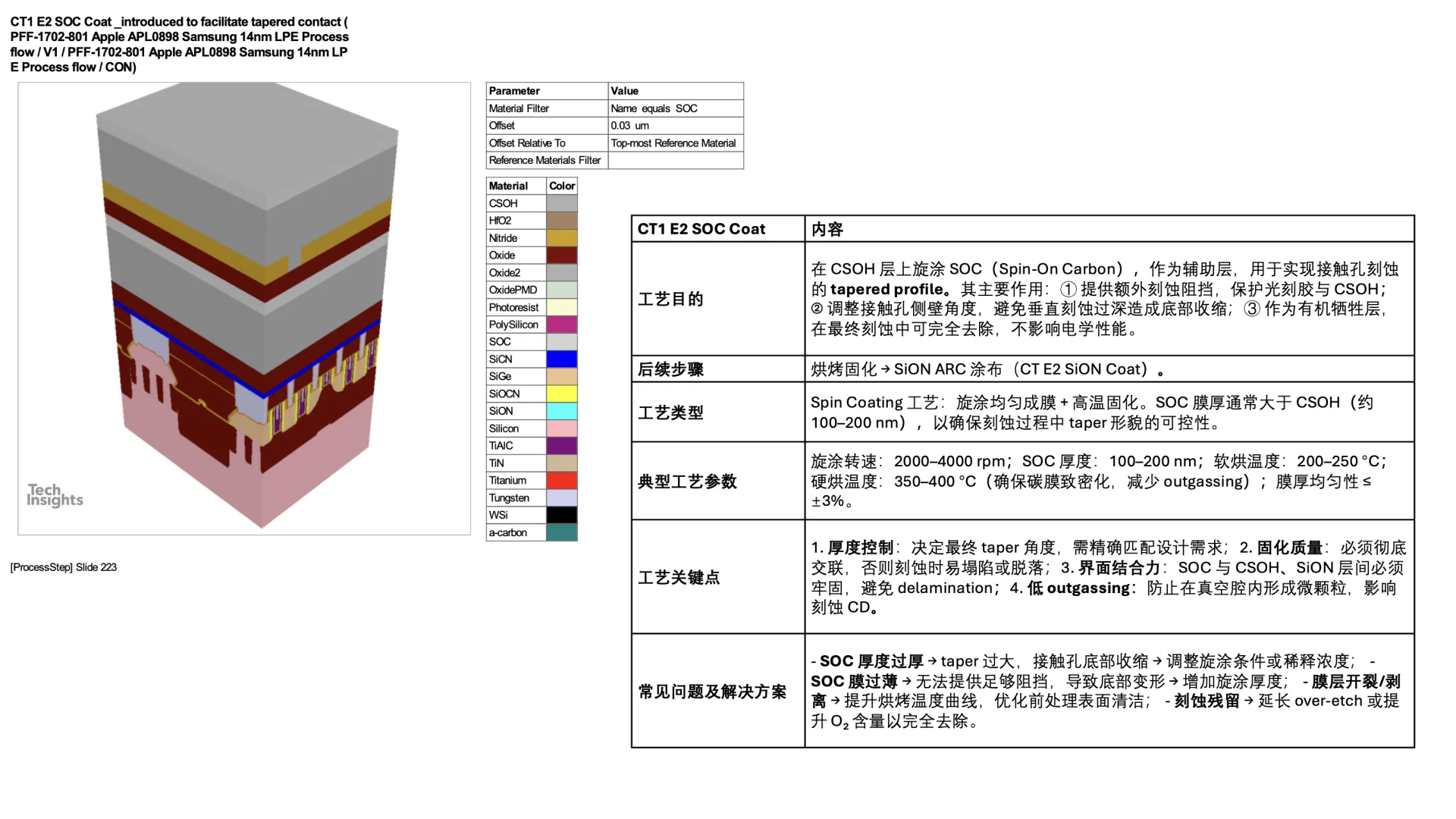

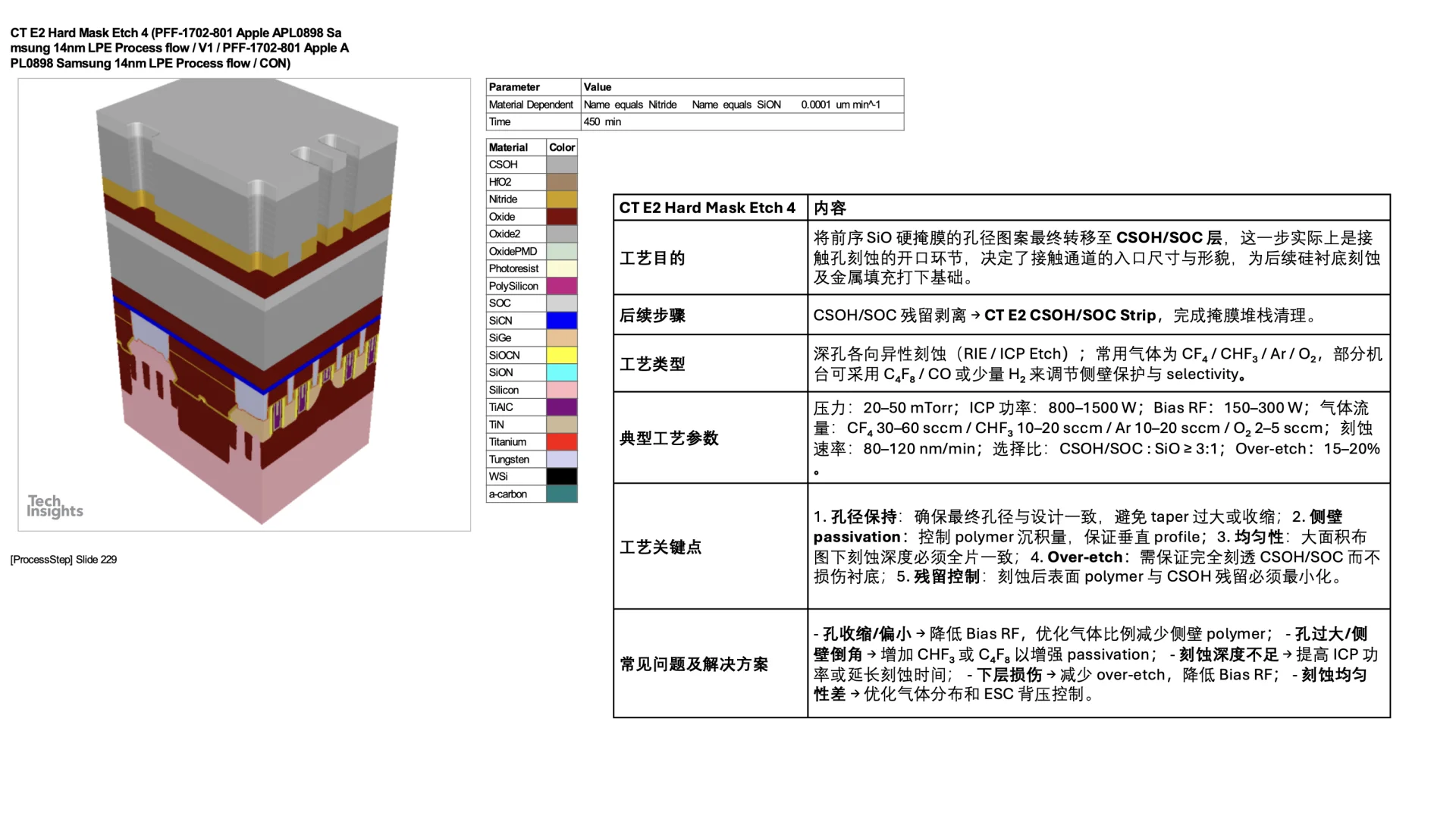

通过 CSOH、SOC、SiON 等多层涂布与硬掩膜形成,提供高选择比与刻蚀保护。

SOC 的引入在这一代工艺中尤为关键,用于改善 taper,避免接触孔因过度各向异性而出现形变或塌陷。

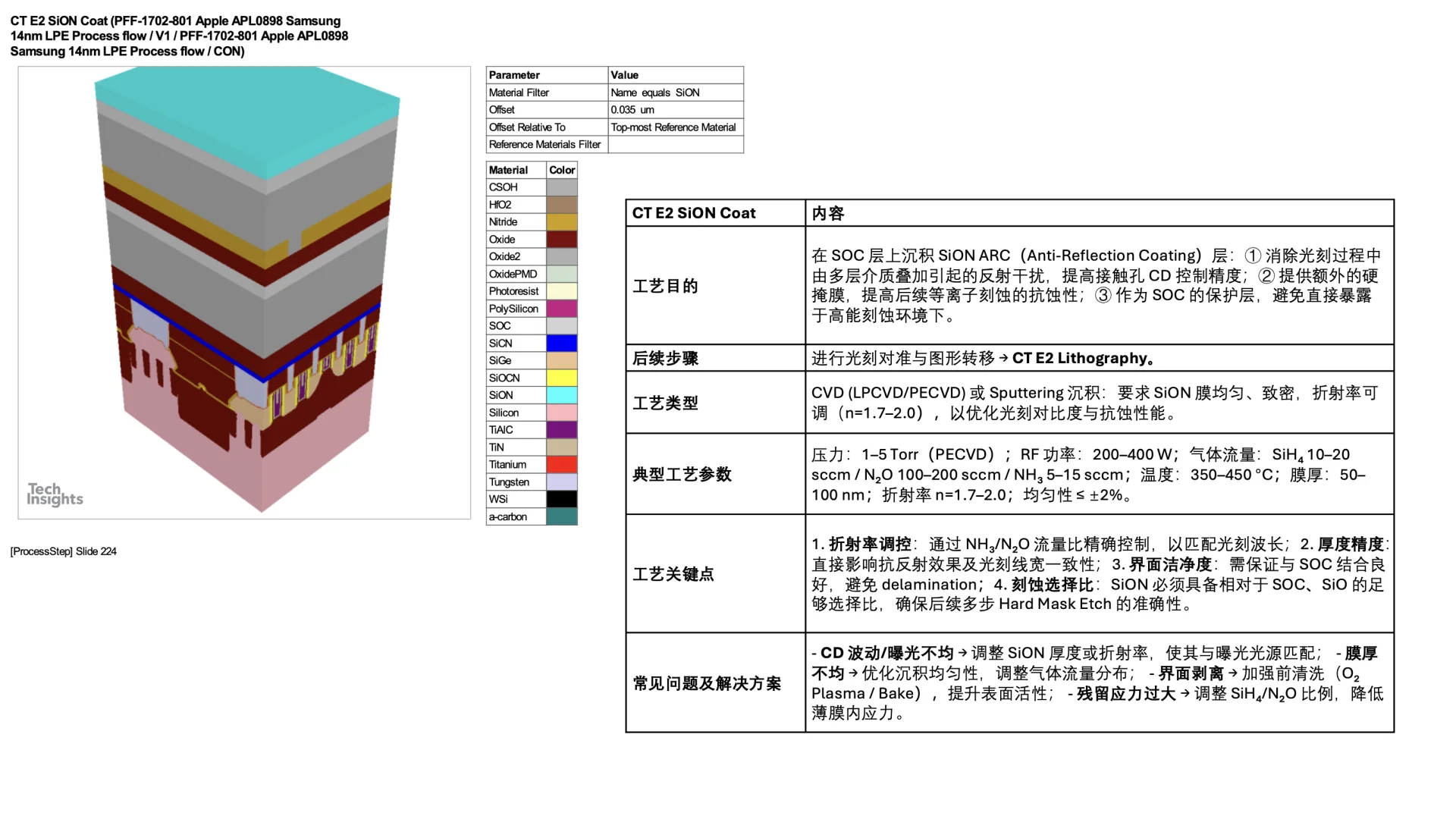

图形定义与传递

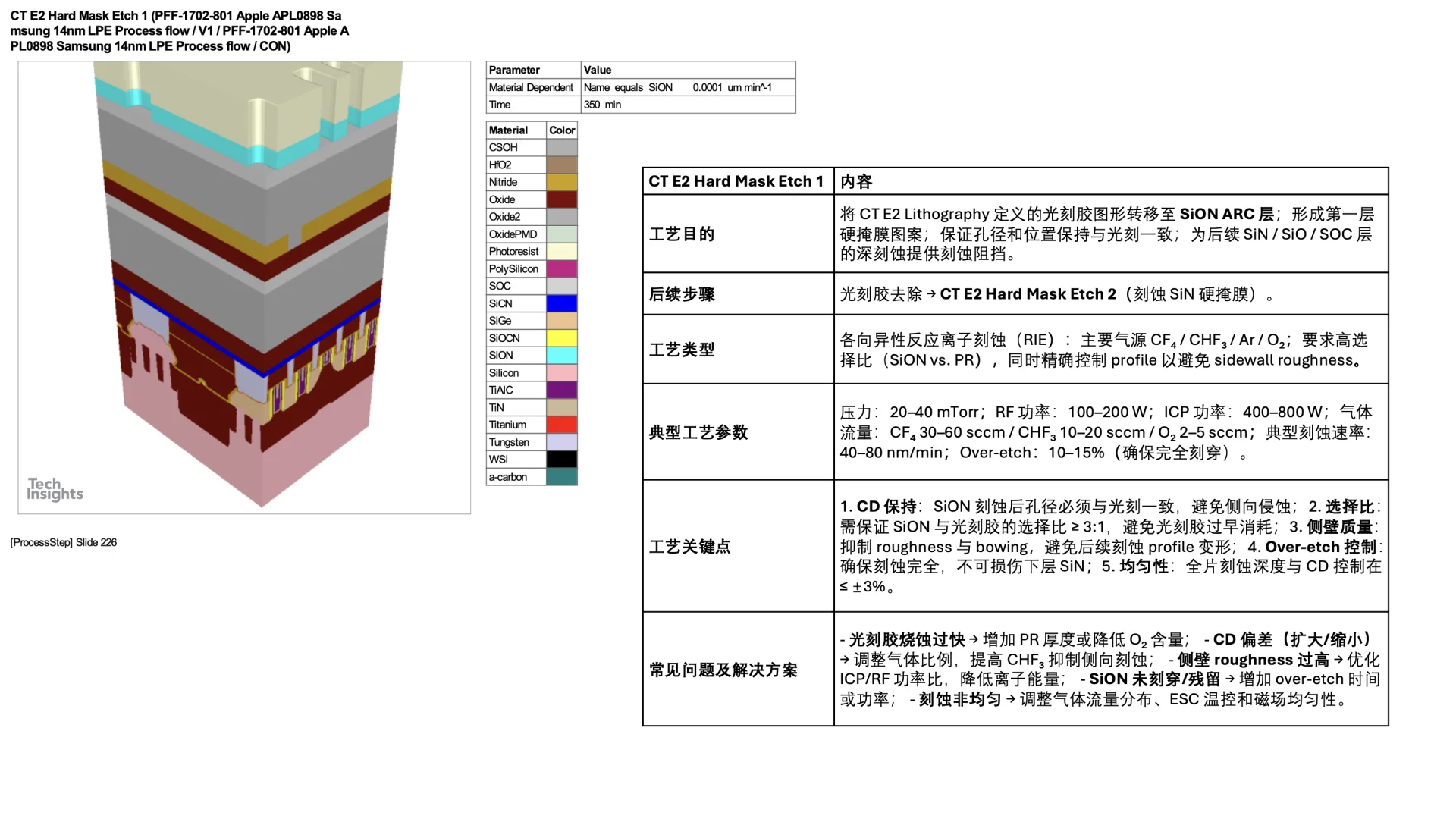

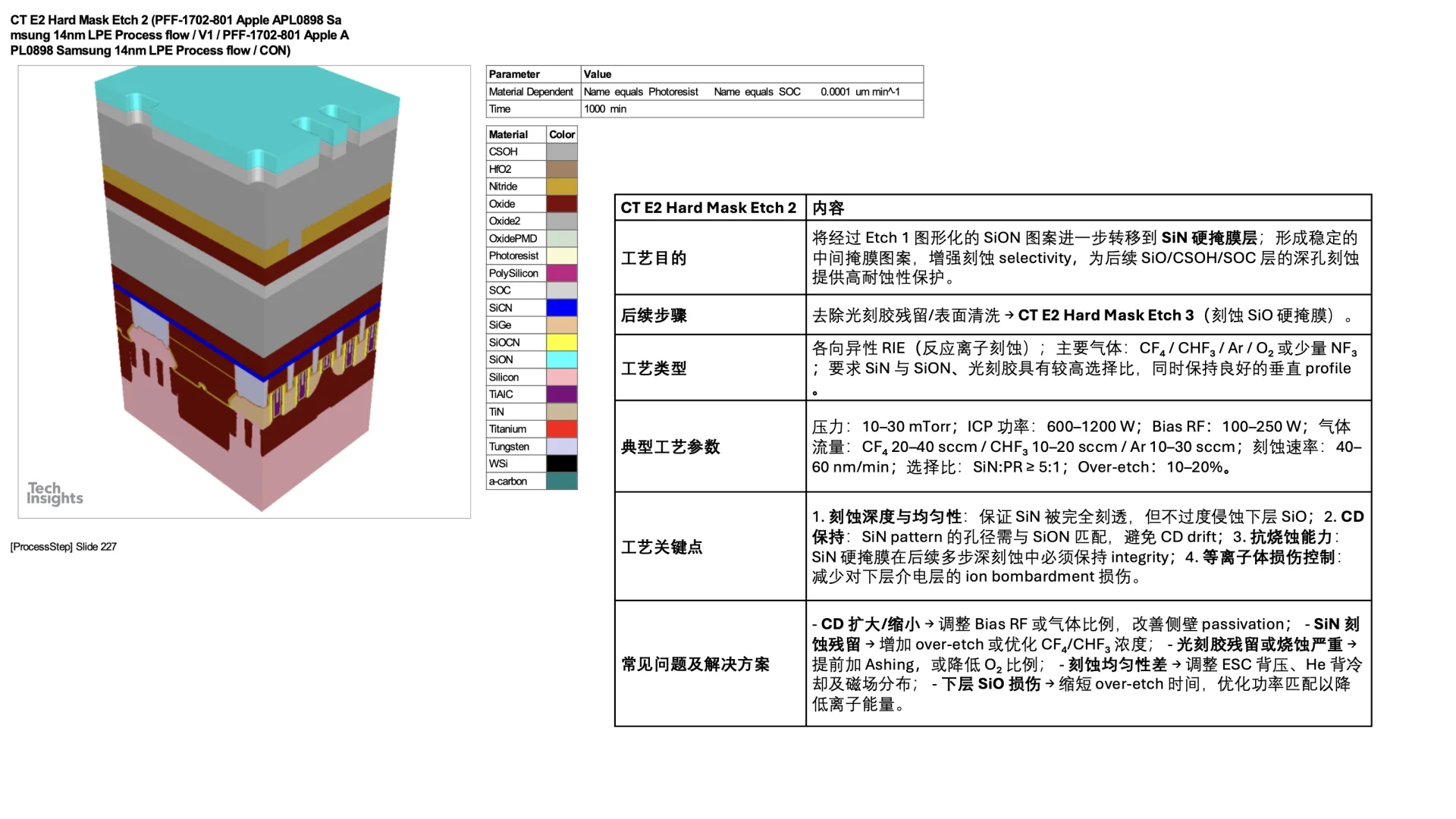

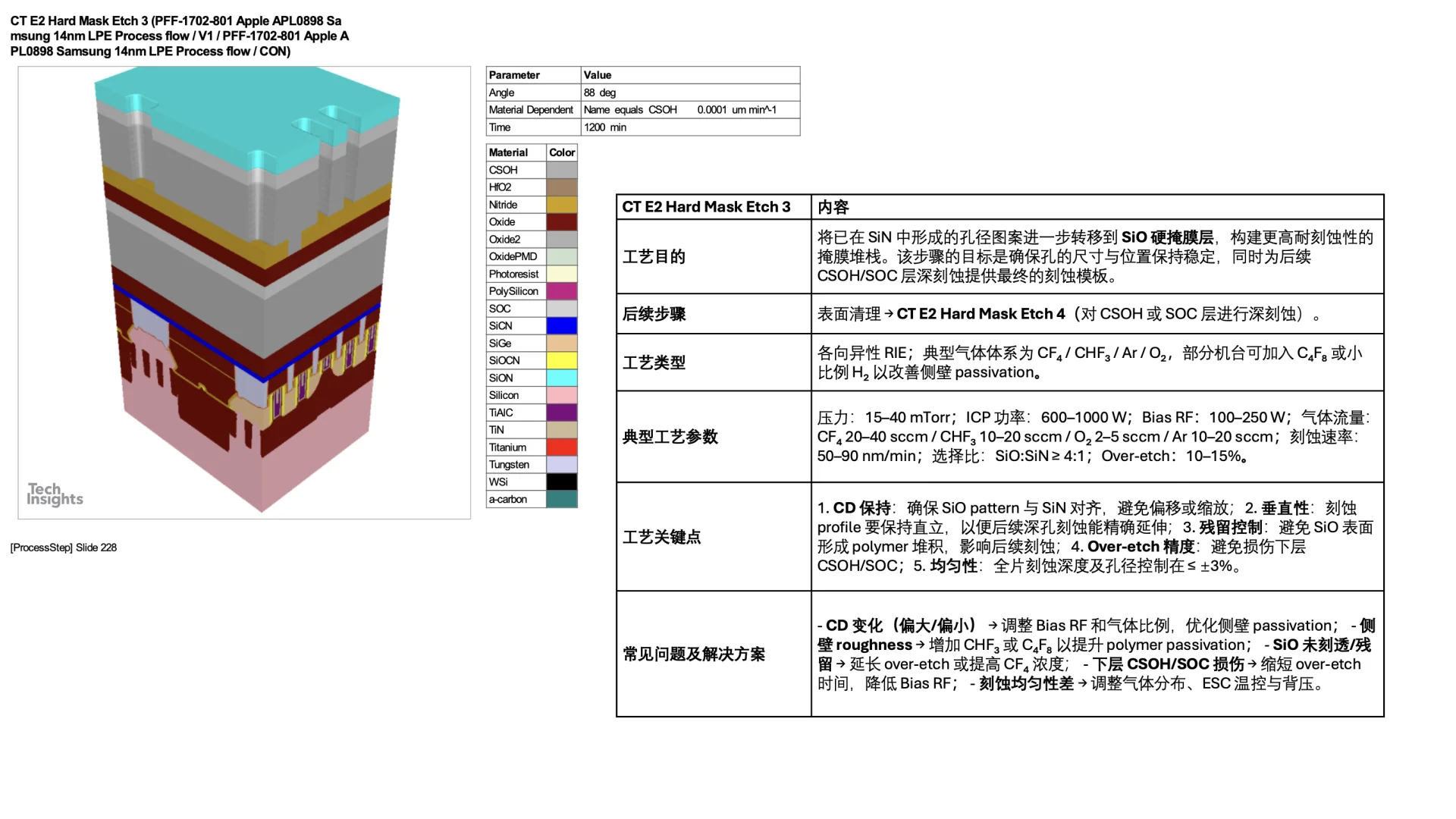

光刻定义接触窗口位置,随后分阶段(Etch 1 → Etch 4)将图形逐步转移至硬掩膜。

多步硬掩膜刻蚀的核心是控制各层的 selectivity 与 profile,确保后续主刻蚀(silicon/contact etch)时窗口尺寸精准。

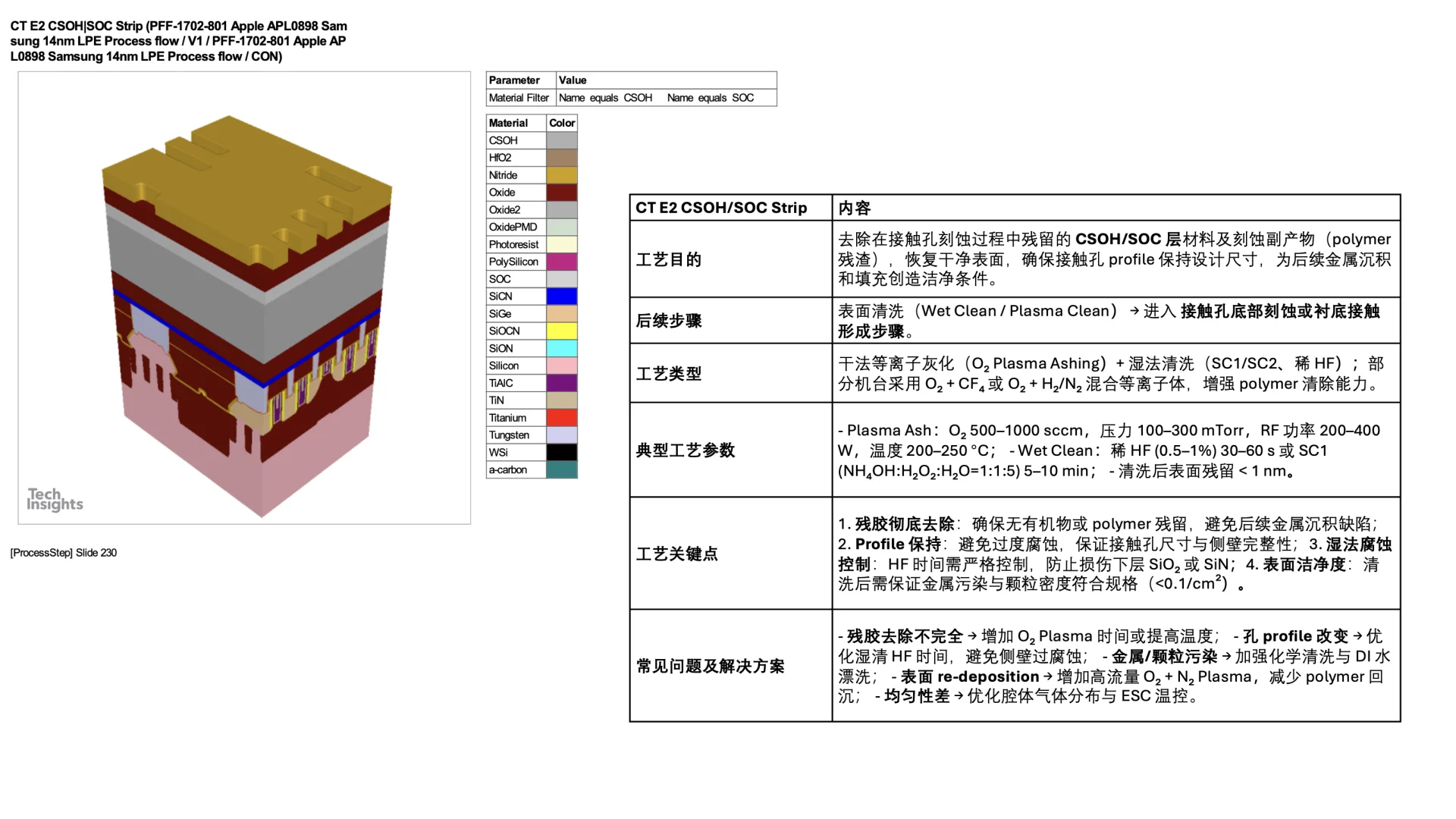

清理与去除

通过 CSOH | SOC Strip 去除光刻胶与辅助涂层,避免残留影响电学性能。

同时对硬掩膜侧壁进行修整,减少 line edge roughness(LER)和接触电阻不稳定性。

关键价值

高纵深比接触孔形成:确保 14nm 节点下的接触电阻可控。

工艺窗口拓展:SOC 的引入和多步硬掩膜刻蚀提升了 pattern transfer 的稳健性。

后续兼容性:为金属填充(如 W CVD)与 CMP 打下平整基础,降低缺陷率。

这一阶段本质上是 “图形控制 + 硬掩膜管理 + 清理优化” 的组合拳,用来保证 接触窗口的高精度定义。没有 SOC 的 taper 改善与多步硬掩膜刻蚀,14nm 节点下的接触孔会很难维持可靠的 profile 和一致性。#14nm制程 #半导体 #芯片 #电子元器件

材料堆叠

通过 CSOH、SOC、SiON 等多层涂布与硬掩膜形成,提供高选择比与刻蚀保护。

SOC 的引入在这一代工艺中尤为关键,用于改善 taper,避免接触孔因过度各向异性而出现形变或塌陷。

图形定义与传递

光刻定义接触窗口位置,随后分阶段(Etch 1 → Etch 4)将图形逐步转移至硬掩膜。

多步硬掩膜刻蚀的核心是控制各层的 selectivity 与 profile,确保后续主刻蚀(silicon/contact etch)时窗口尺寸精准。

清理与去除

通过 CSOH | SOC Strip 去除光刻胶与辅助涂层,避免残留影响电学性能。

同时对硬掩膜侧壁进行修整,减少 line edge roughness(LER)和接触电阻不稳定性。

关键价值

高纵深比接触孔形成:确保 14nm 节点下的接触电阻可控。

工艺窗口拓展:SOC 的引入和多步硬掩膜刻蚀提升了 pattern transfer 的稳健性。

后续兼容性:为金属填充(如 W CVD)与 CMP 打下平整基础,降低缺陷率。

这一阶段本质上是 “图形控制 + 硬掩膜管理 + 清理优化” 的组合拳,用来保证 接触窗口的高精度定义。没有 SOC 的 taper 改善与多步硬掩膜刻蚀,14nm 节点下的接触孔会很难维持可靠的 profile 和一致性。#14nm制程 #半导体 #芯片 #电子元器件