在14nm FinFET制程中,M2层(Metal 2)互连结构是金属互连系统中的第二层导线,承担着跨模块信号传输与电源分配的关键功能。其工艺控制要求极高,涉及多层介电材料沉积、光刻刻蚀及金属填充等核心环节。该阶段的重点在于兼顾高精度图形定义、低介电常数控制与可靠金属接触形成。

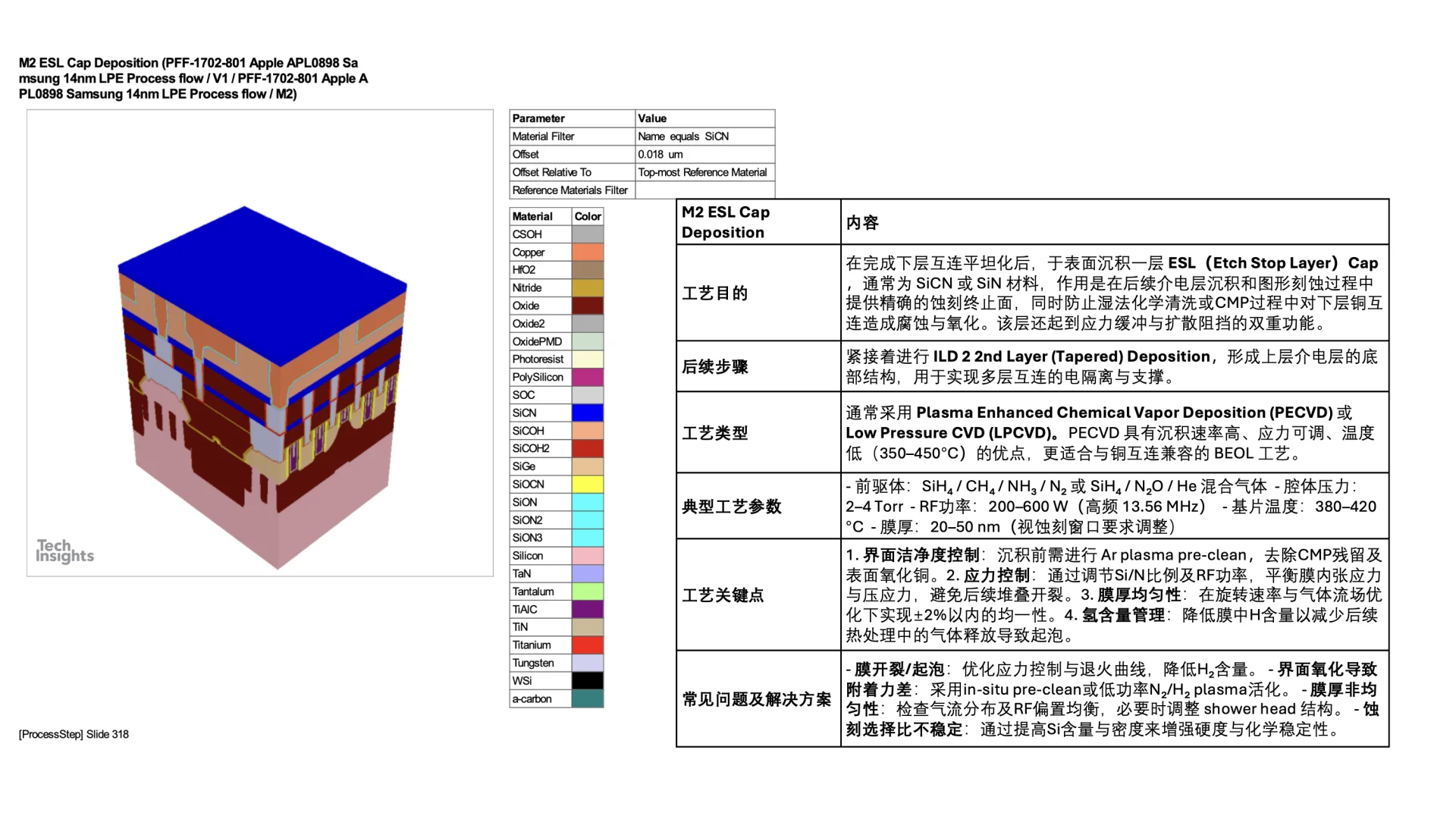

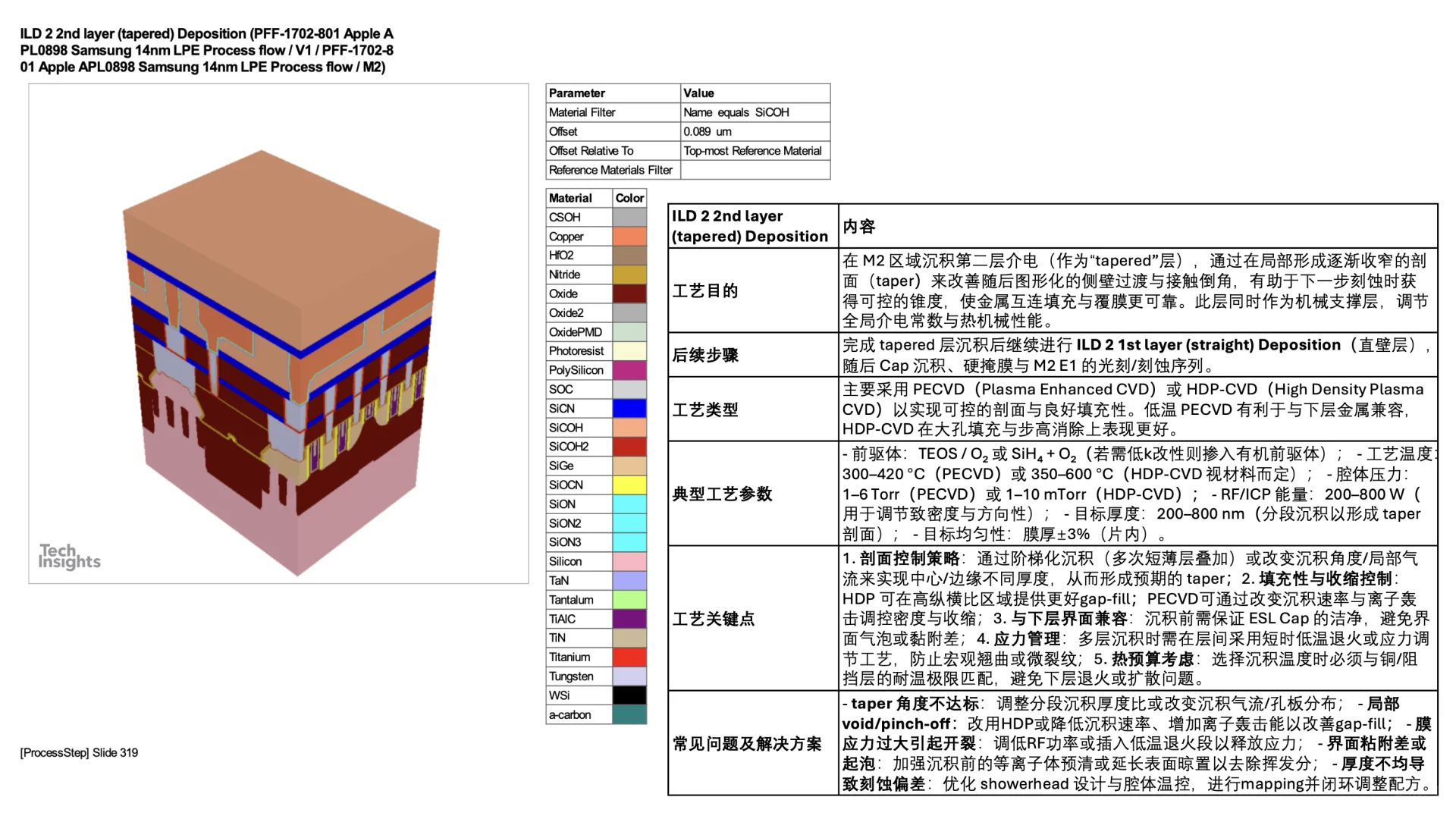

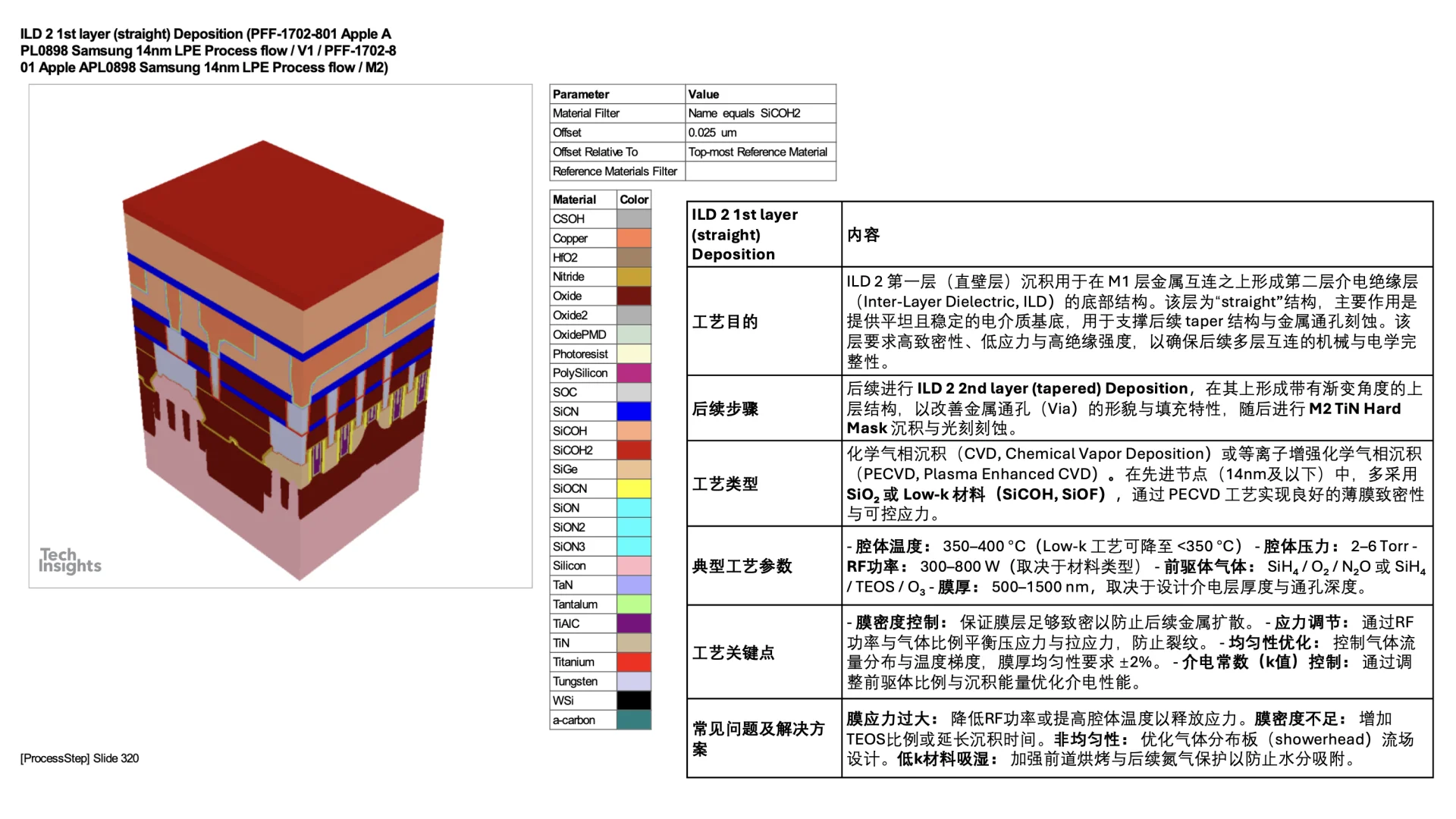

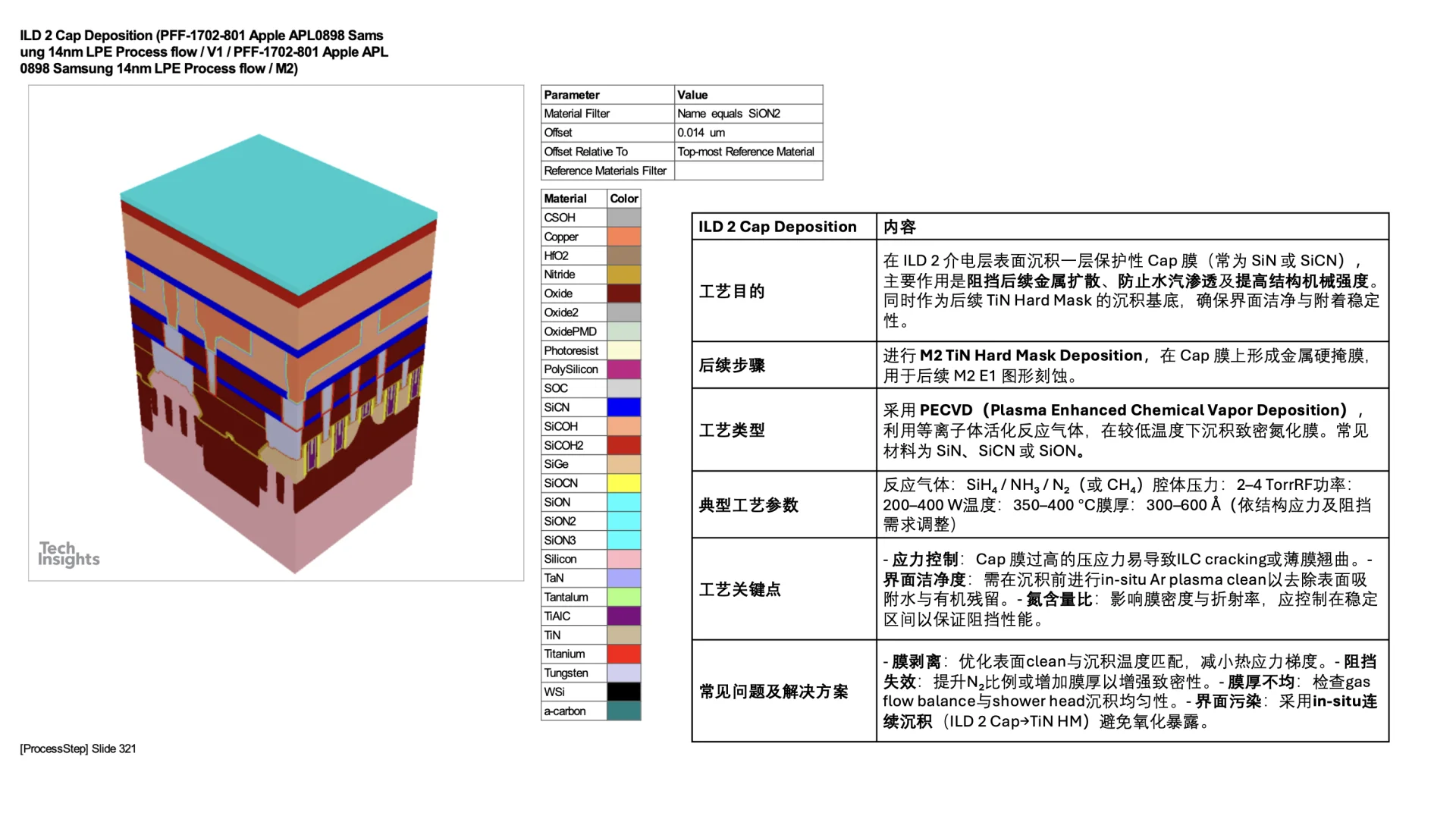

首先,M2 ESL Cap Deposition 为M1层铜互连提供阻挡与应力释放功能,采用SiCN或SiN薄膜,兼具防铜扩散与机械稳定性。随后通过 ILD 2双层结构沉积(straight + tapered),形成第二层介电层的主体。直壁层(straight layer)保证结构平整与介电完整性,而上层的tapered层通过几何形貌优化,使后续通孔(via)刻蚀具有良好的锥形侧壁,利于金属填充并减少空洞。

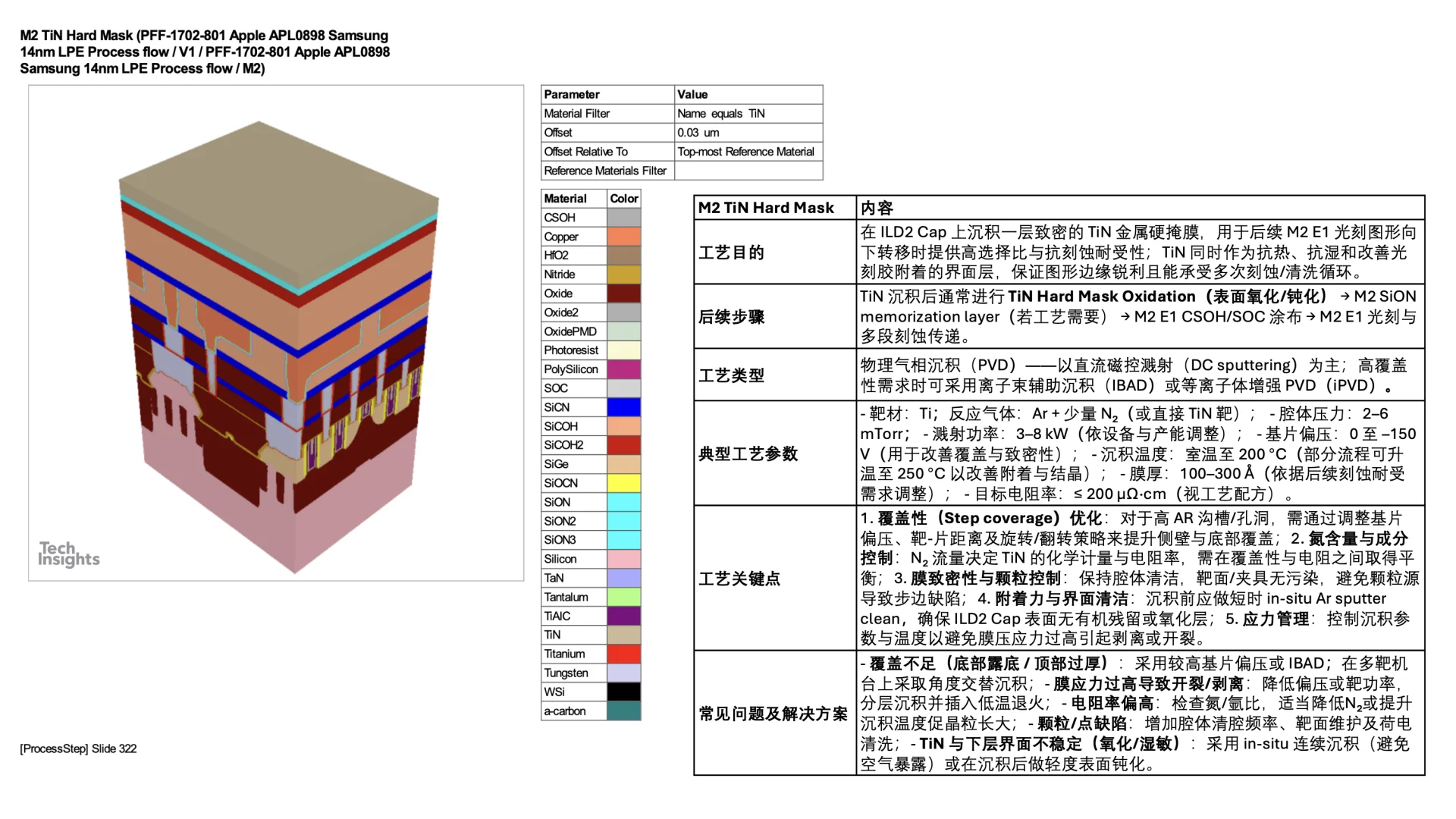

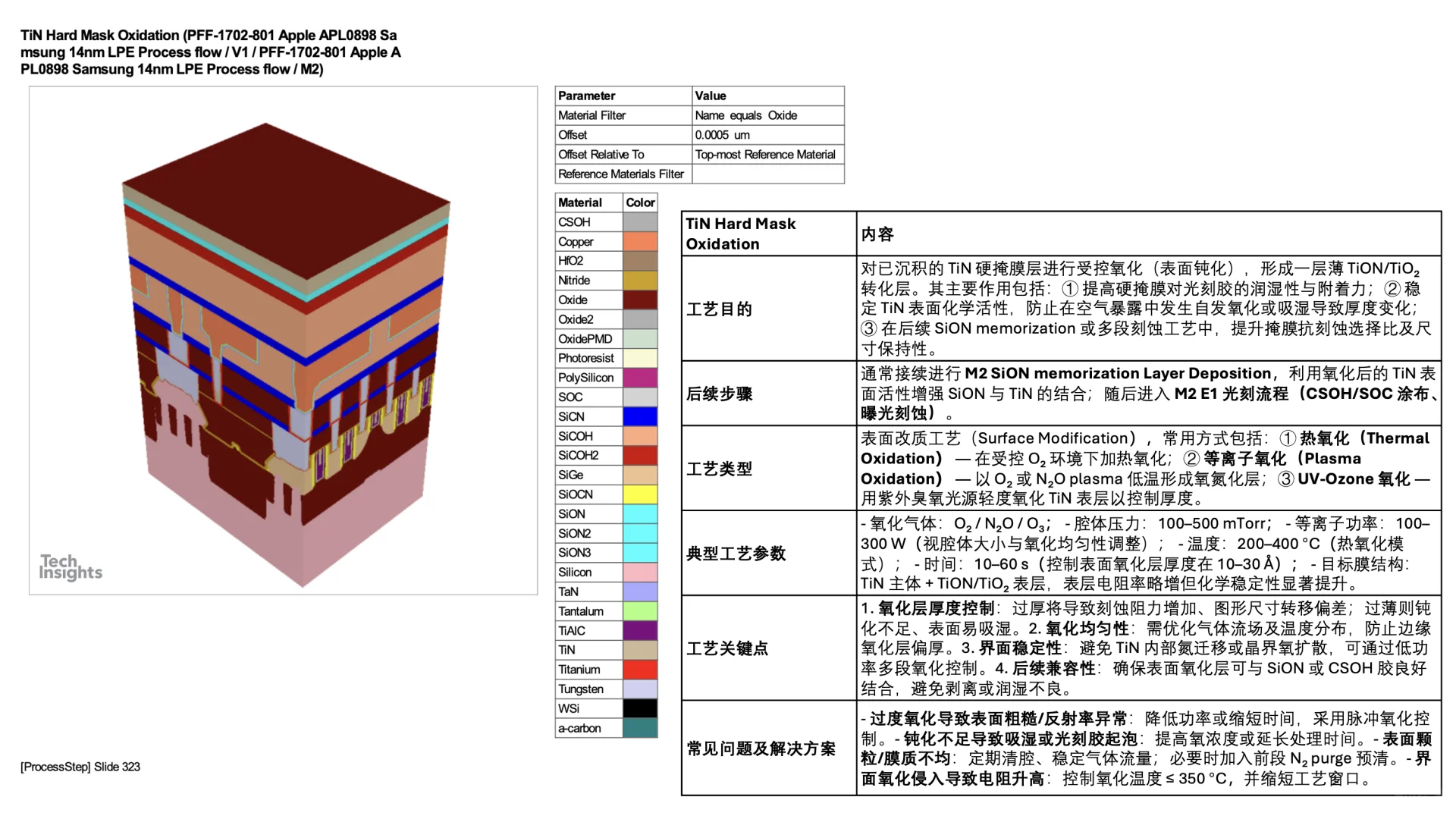

接着,M2 TiN Hard Mask 与 TiN Hard Mask Oxidation 步骤在图形化环节中起到关键作用。TiN作为硬掩膜材料具备高刻蚀选择比与优异的尺寸控制性,其表面氧化处理可进一步提升与光刻胶(PR)及介质层的附着性,并改善刻蚀侧壁的抗反射性能。

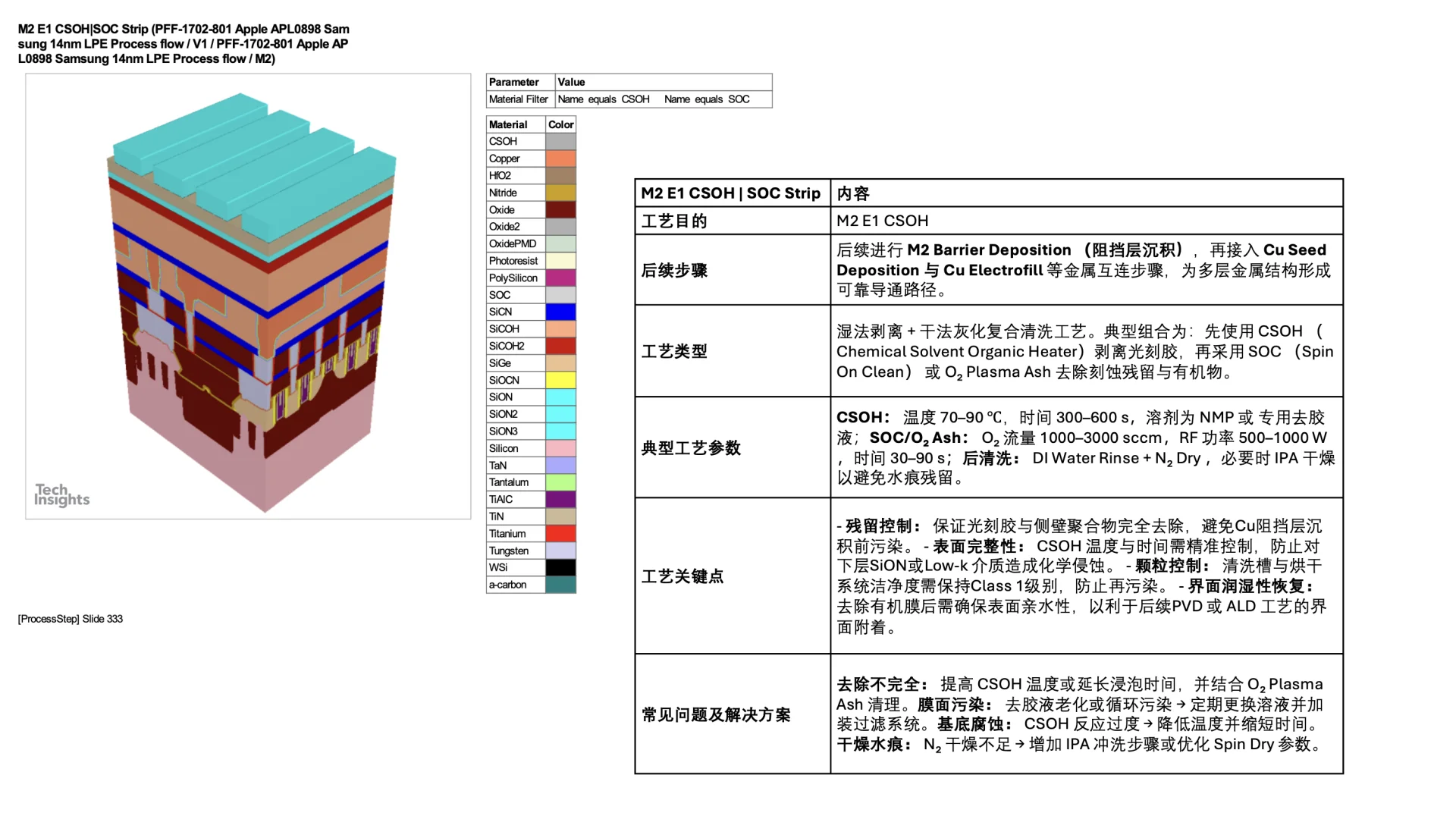

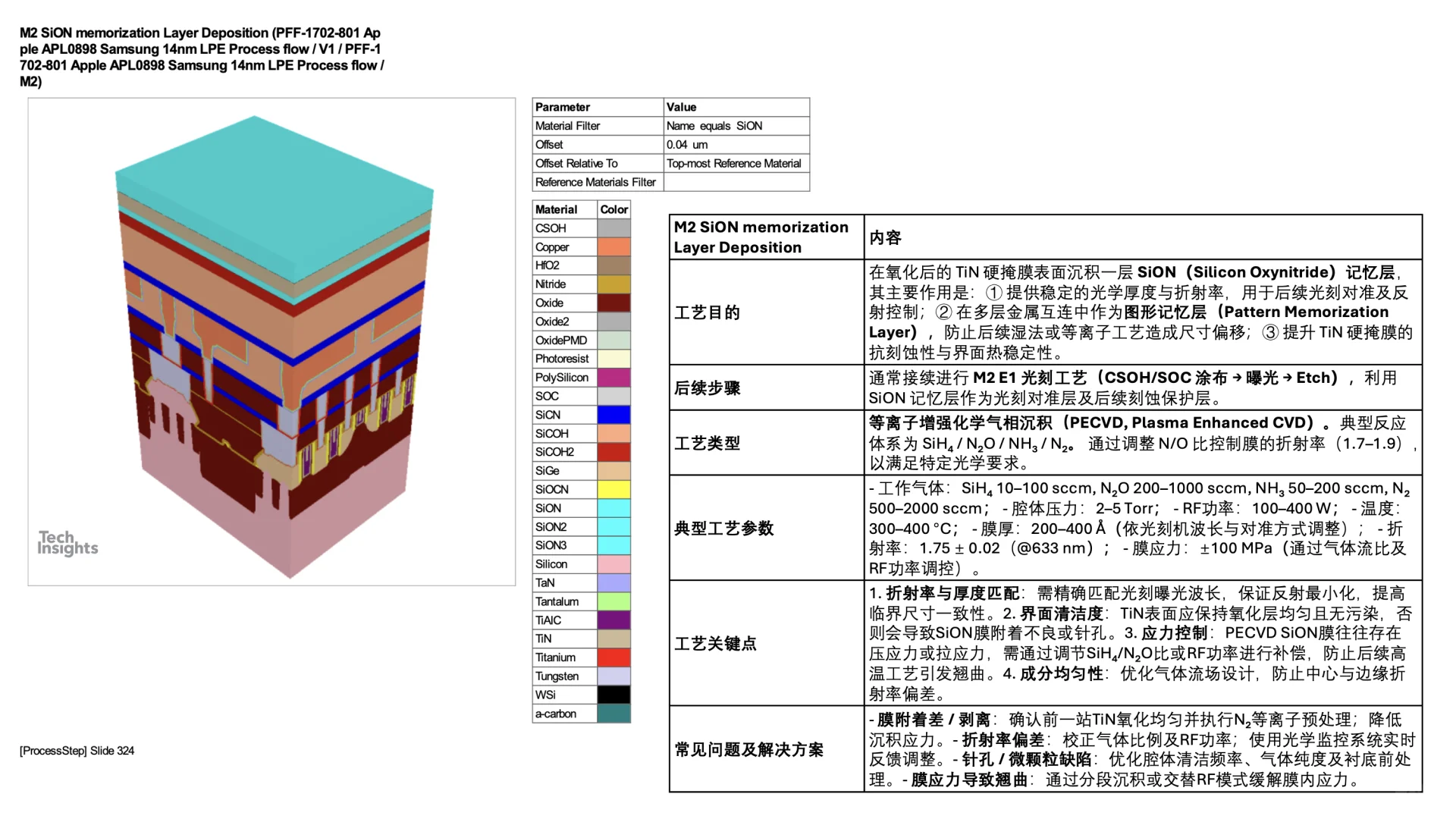

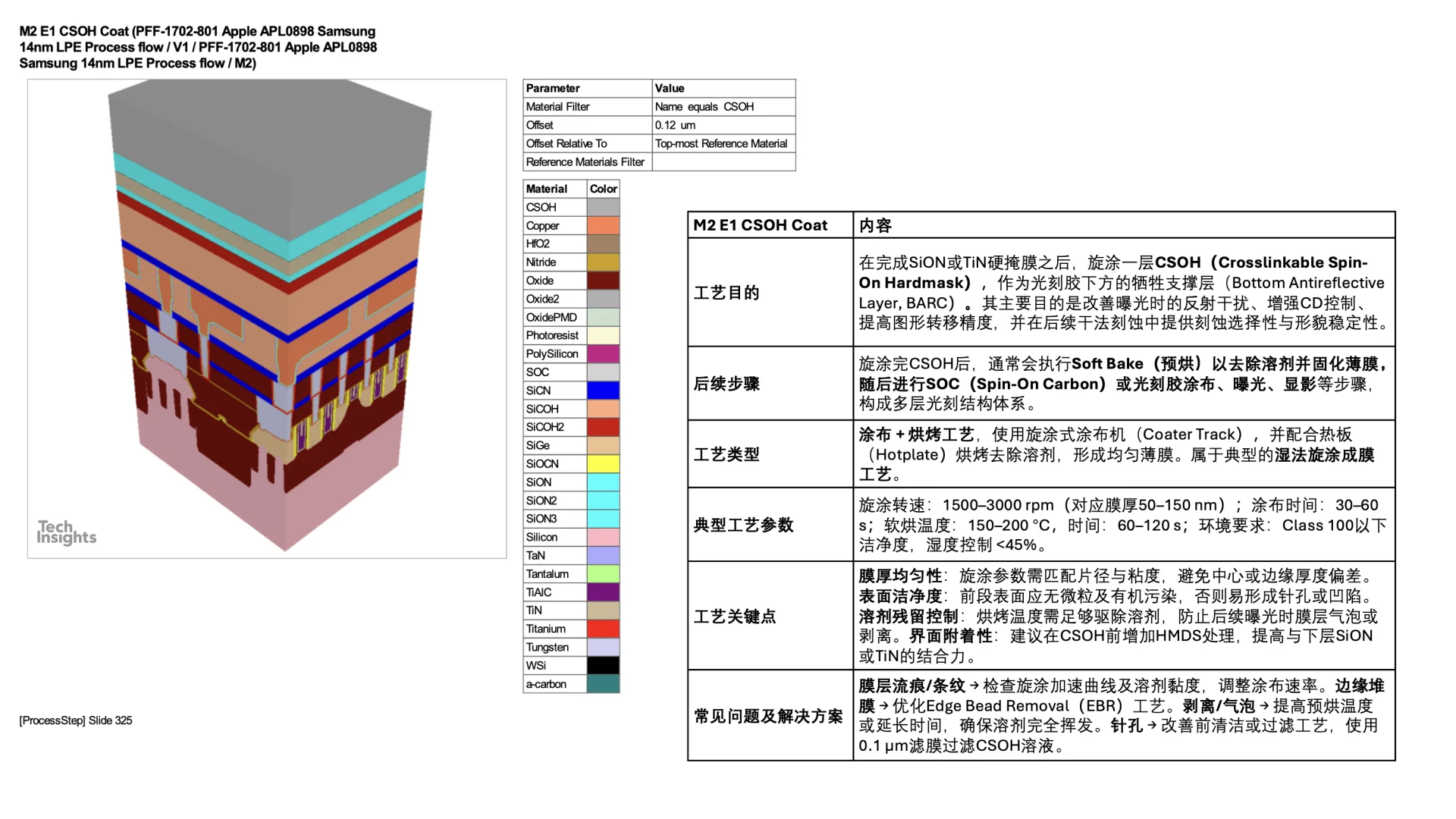

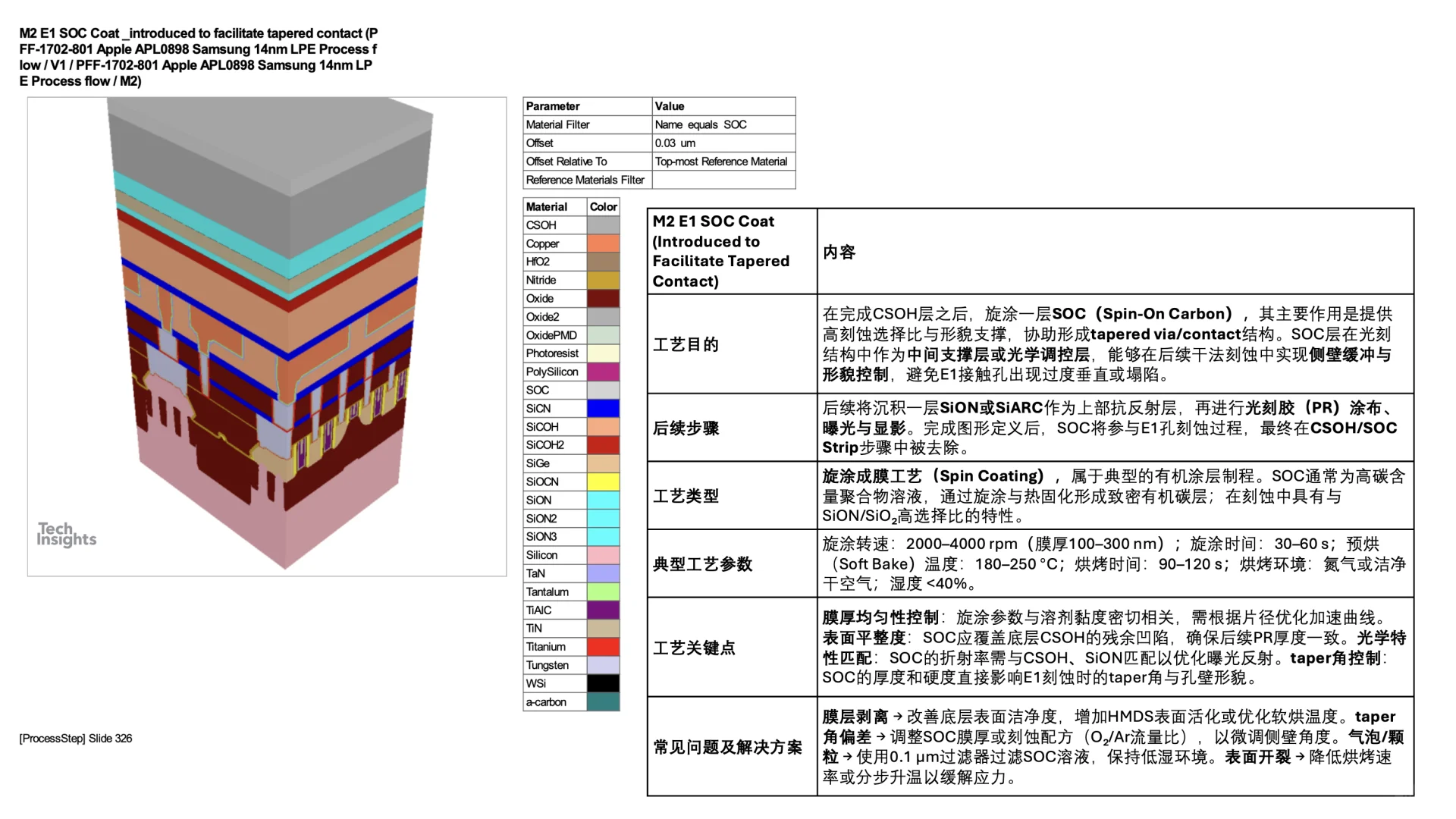

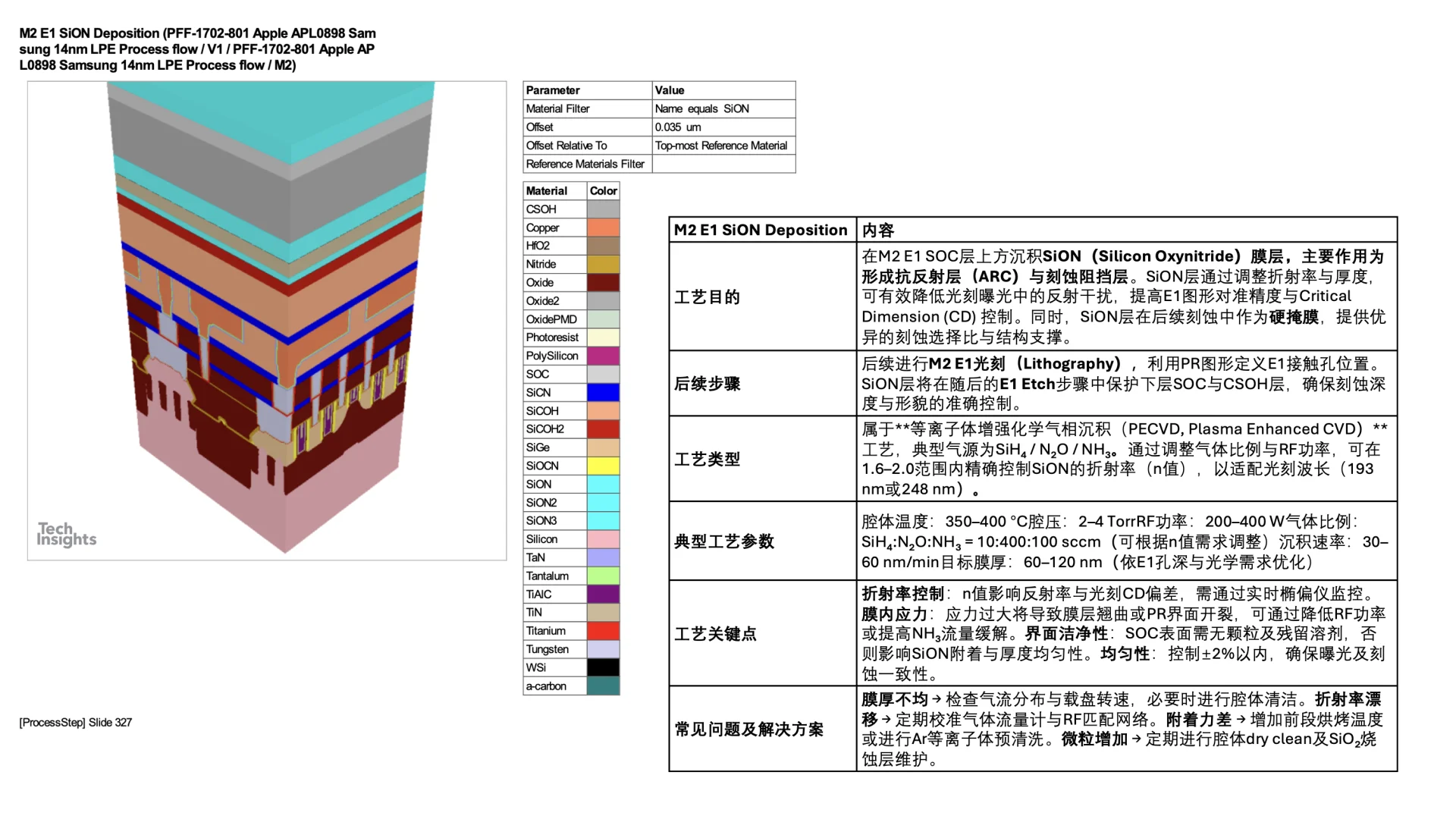

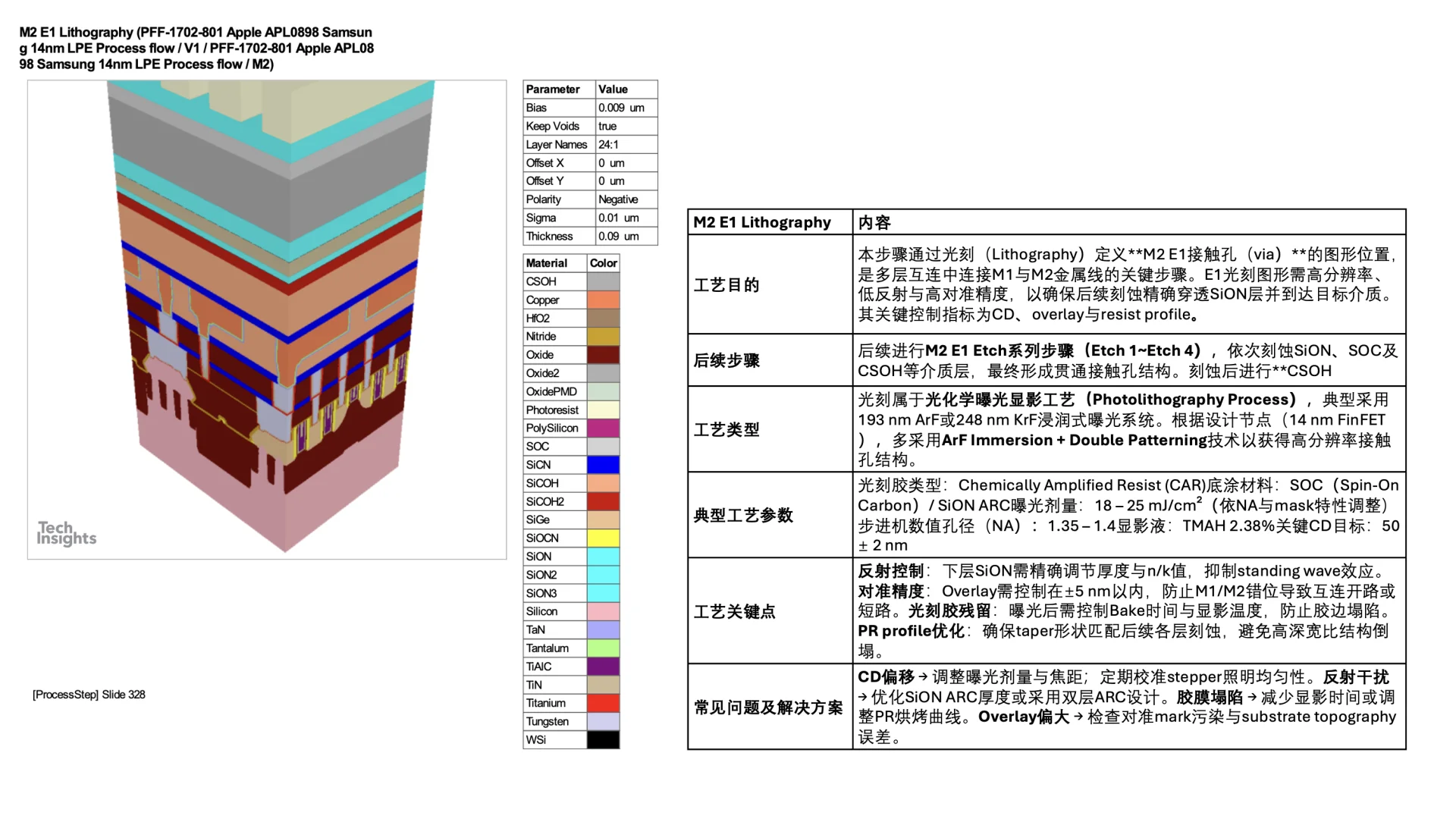

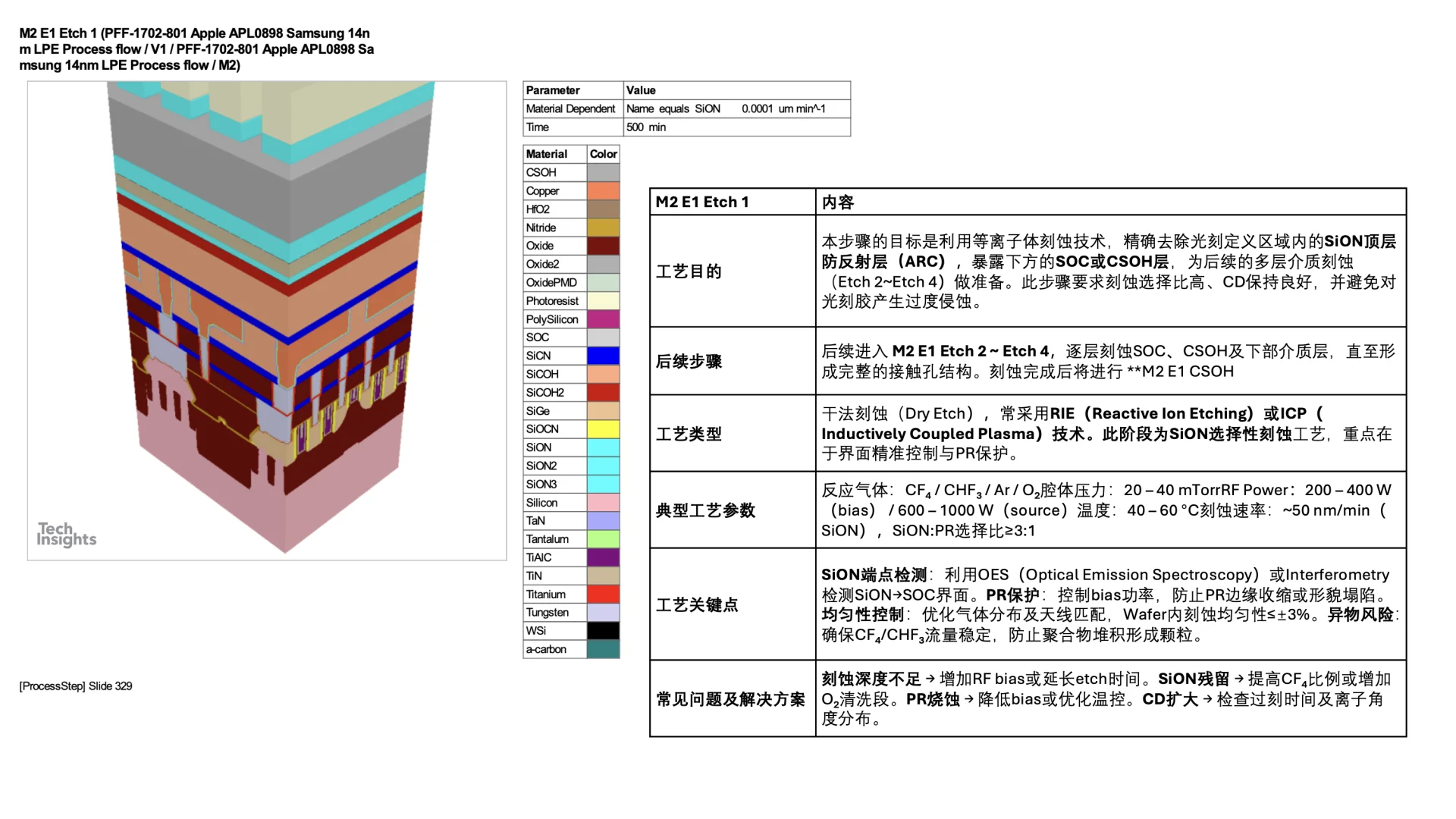

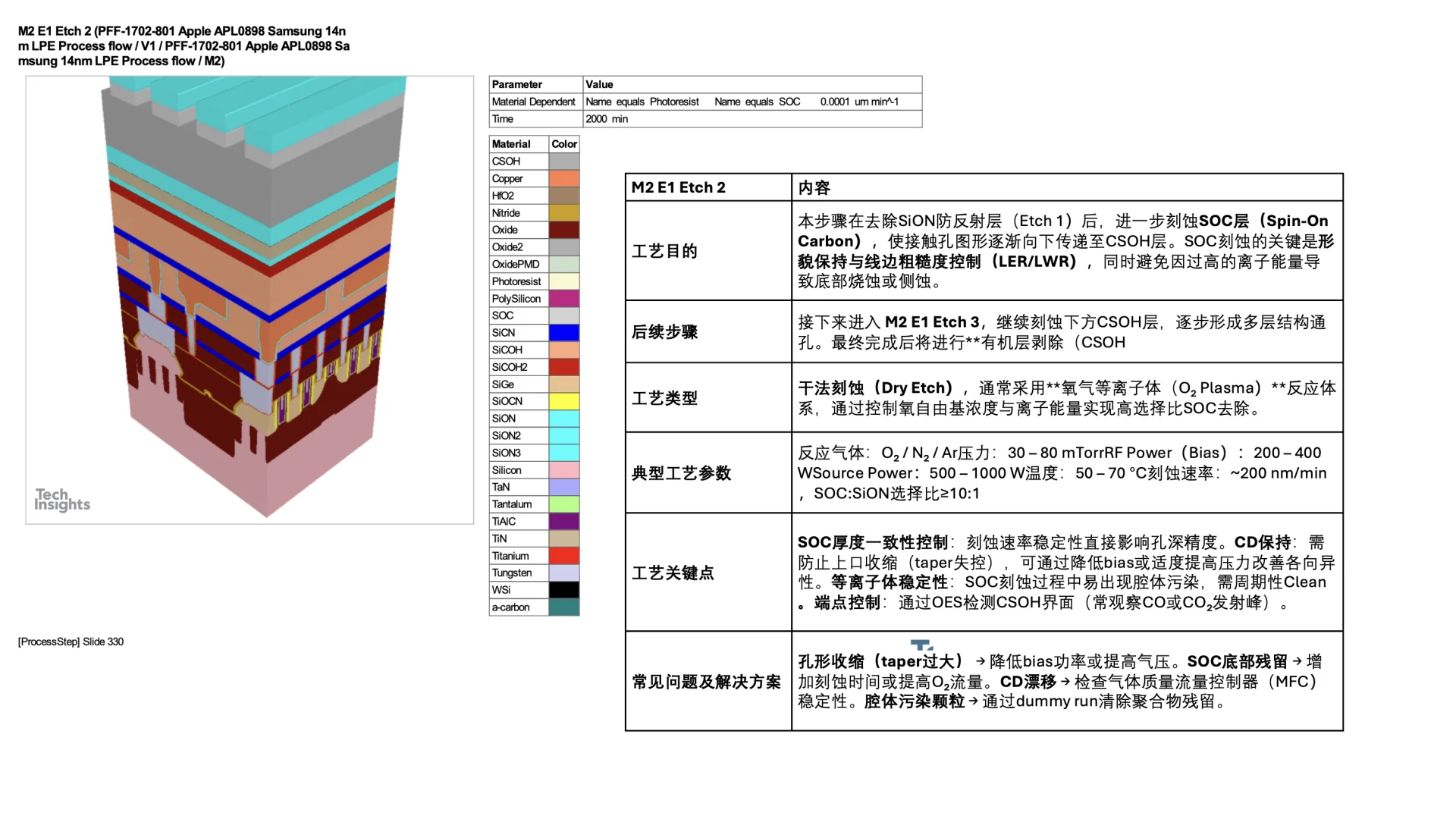

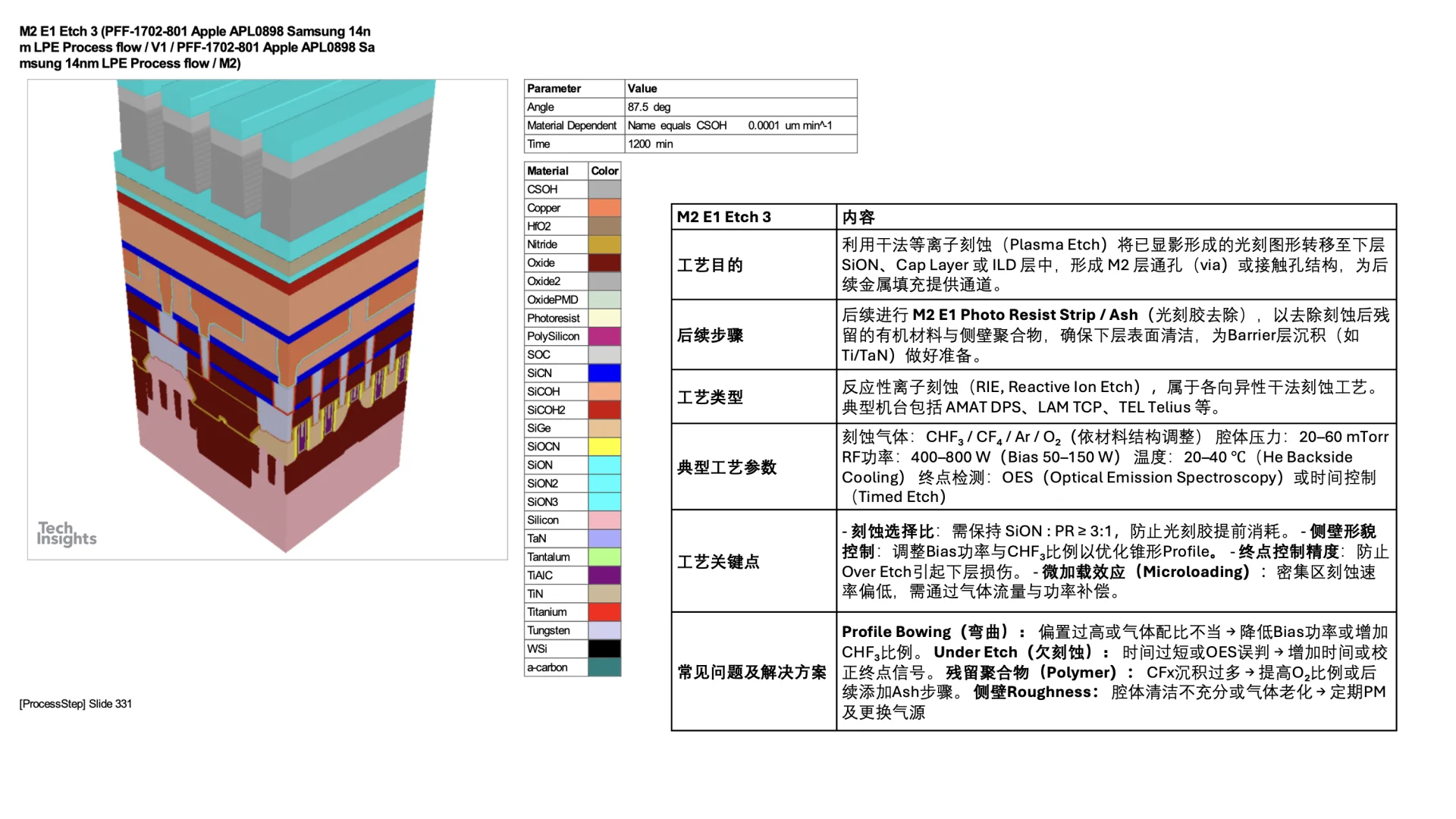

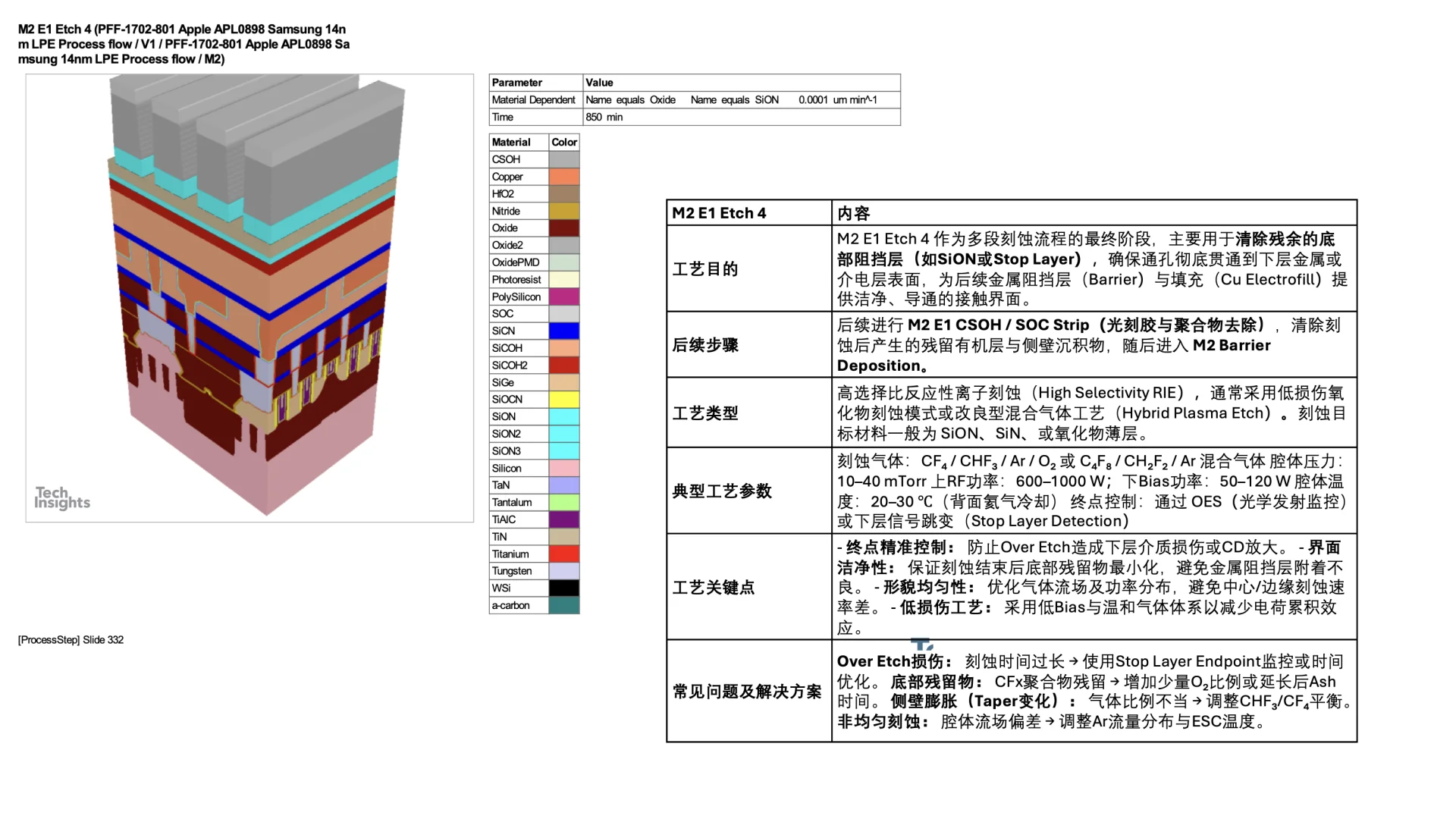

在图形化阶段,M2 E1 CSOH Coat / SOC Coat / SiON Deposition / Lithography / Etch 系列步骤构成了整个M2层的patterning核心流程。CSOH(spin-on carbon hardmask)与SOC(spin-on oxide coating)通过多层结构组合实现高深宽比通孔的形貌控制。SiON层则作为抗反射涂层(BARC),用于优化光刻分辨率与减少反射干扰。此阶段的刻蚀(Etch 1–4)需精准控制刻蚀深度与侧壁角度,以确保via与trench对准及电阻均一性。最后,CSOH/SOC Strip 通过氧等离子体灰化(O₂ Ash)或湿法去除,确保清洁的通孔底部,为后续Barrier/TaN及Cu填充提供洁净界面。

总体而言,M2层的关键在于实现高纵深图形的一致性控制与低介电常数介质的可靠保护。该模块的每一步都影响最终互连电阻、延迟及可靠性,任何膜厚偏差、应力异常或刻蚀形貌偏移,都可能导致互连失效或信号时序偏差。因此,M2模块不仅体现了多材料协同的工艺深度,也代表了FinFET后段制程的综合精密水平。#14nm制程 #半导体 #电子元器件 #芯片

首先,M2 ESL Cap Deposition 为M1层铜互连提供阻挡与应力释放功能,采用SiCN或SiN薄膜,兼具防铜扩散与机械稳定性。随后通过 ILD 2双层结构沉积(straight + tapered),形成第二层介电层的主体。直壁层(straight layer)保证结构平整与介电完整性,而上层的tapered层通过几何形貌优化,使后续通孔(via)刻蚀具有良好的锥形侧壁,利于金属填充并减少空洞。

接着,M2 TiN Hard Mask 与 TiN Hard Mask Oxidation 步骤在图形化环节中起到关键作用。TiN作为硬掩膜材料具备高刻蚀选择比与优异的尺寸控制性,其表面氧化处理可进一步提升与光刻胶(PR)及介质层的附着性,并改善刻蚀侧壁的抗反射性能。

在图形化阶段,M2 E1 CSOH Coat / SOC Coat / SiON Deposition / Lithography / Etch 系列步骤构成了整个M2层的patterning核心流程。CSOH(spin-on carbon hardmask)与SOC(spin-on oxide coating)通过多层结构组合实现高深宽比通孔的形貌控制。SiON层则作为抗反射涂层(BARC),用于优化光刻分辨率与减少反射干扰。此阶段的刻蚀(Etch 1–4)需精准控制刻蚀深度与侧壁角度,以确保via与trench对准及电阻均一性。最后,CSOH/SOC Strip 通过氧等离子体灰化(O₂ Ash)或湿法去除,确保清洁的通孔底部,为后续Barrier/TaN及Cu填充提供洁净界面。

总体而言,M2层的关键在于实现高纵深图形的一致性控制与低介电常数介质的可靠保护。该模块的每一步都影响最终互连电阻、延迟及可靠性,任何膜厚偏差、应力异常或刻蚀形貌偏移,都可能导致互连失效或信号时序偏差。因此,M2模块不仅体现了多材料协同的工艺深度,也代表了FinFET后段制程的综合精密水平。#14nm制程 #半导体 #电子元器件 #芯片